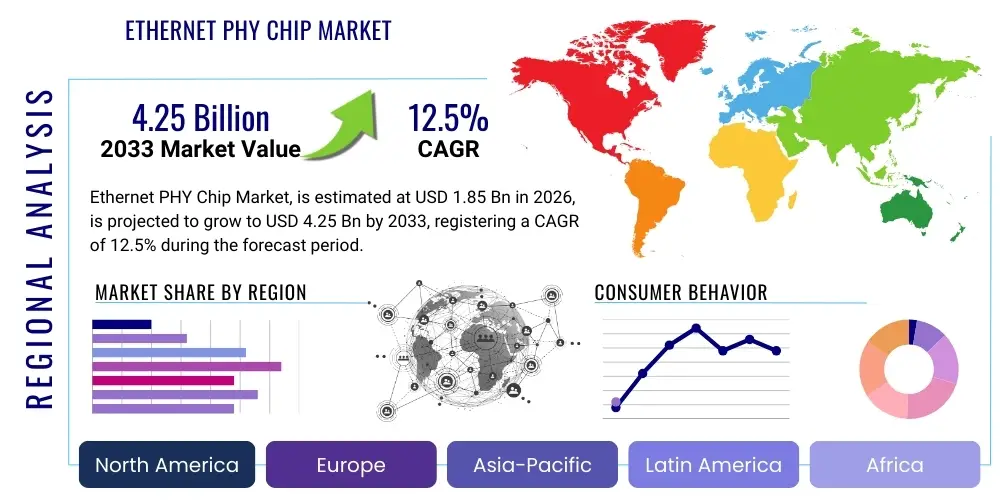

Ethernet PHY Chip Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 436108 | Date : Dec, 2025 | Pages : 246 | Region : Global | Publisher : MRU

Ethernet PHY Chip Market Size

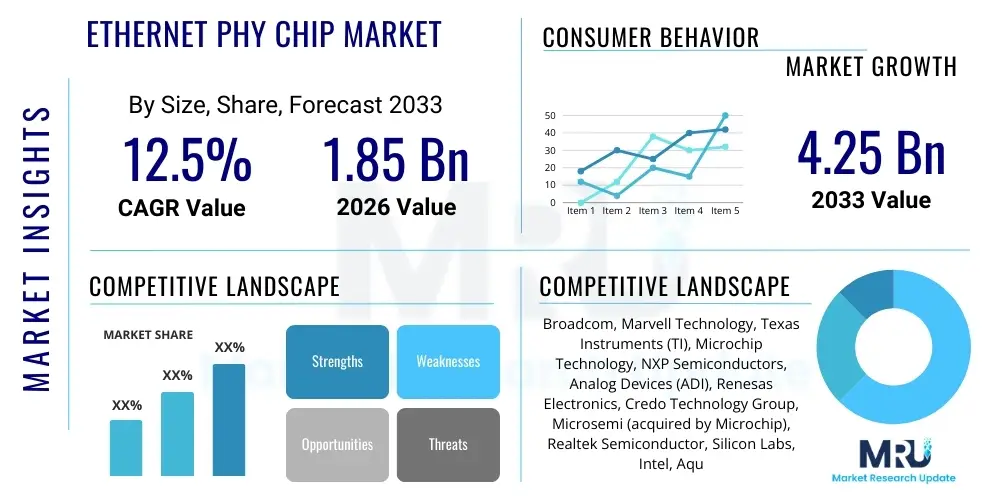

The Ethernet PHY Chip Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 12.5% between 2026 and 2033. The market is estimated at $1.85 Billion in 2026 and is projected to reach $4.25 Billion by the end of the forecast period in 2033.

Ethernet PHY Chip Market introduction

The Ethernet Physical Layer (PHY) chip is a crucial component in all network devices, serving as the interface between the Media Access Control (MAC) layer of a system and the physical transmission medium (such as copper cables or fiber optics). Its primary function is to handle the physical encoding and decoding of data signals, ensuring reliable communication over the network infrastructure. These chips are instrumental in enabling the interoperability and high-speed data transmission required by modern communication standards, ranging from 10 Megabits per second (Mbps) to ultra-high 800 Gigabits per second (Gbps) links found in advanced data centers.

Major applications of Ethernet PHY chips span across several rapidly evolving sectors, including enterprise networking equipment (switches, routers), data centers, industrial automation, and the burgeoning automotive sector, particularly in advanced driver-assistance systems (ADAS) and in-vehicle infotainment. The escalating demand for bandwidth and low-latency communication, driven by cloud computing, Internet of Things (IoT) expansion, and high-definition media streaming, acts as a pivotal driving factor. Furthermore, the integration of Power over Ethernet (PoE) capabilities is expanding the utility of these chips in remote device deployment, simplifying infrastructure and reducing installation costs in commercial and industrial settings.

The core benefits derived from advanced Ethernet PHY chips include enhanced signal integrity, lower power consumption, increased data throughput, and greater resilience against environmental noise, which is particularly critical in industrial and automotive applications. The technological shift towards multi-gigabit speeds (2.5G, 5G, 10G) and the miniaturization of components allow for denser deployments and more efficient thermal management in compact systems. This continuous advancement is essential for supporting the next generation of networking infrastructure, cementing the Ethernet PHY chip’s role as a fundamental enabler of global digital transformation and connectivity.

Ethernet PHY Chip Market Executive Summary

The Ethernet PHY Chip Market is experiencing robust growth fueled primarily by the pervasive digitization across all industrial and consumer domains, leading to an unprecedented demand for higher bandwidth and reliable connectivity solutions. Key business trends indicate a strong focus on developing multi-gigabit and high-speed (100G/400G) solutions to cater to hyperscale data centers and demanding AI infrastructure, simultaneously focusing on minimizing power consumption to address operational expenditure concerns. Strategic partnerships between chip manufacturers and network equipment providers are accelerating the adoption of new standards, particularly those relating to Energy Efficient Ethernet (EEE) and automotive-grade robustness, highlighting a market shift towards specialized, high-performance applications rather than generic connectivity.

Regionally, the Asia Pacific (APAC) market dominates in terms of manufacturing capacity and consumption, driven by extensive industrial IoT deployment and the proliferation of consumer electronics, alongside massive investment in 5G infrastructure in countries like China, South Korea, and Japan. North America remains a crucial innovation hub, leading in the deployment of hyperscale data centers and advanced technologies such as 800G Ethernet, while Europe shows steady growth, propelled by strict industrial automation standards and the increasing adoption of Automotive Ethernet standards mandated by regional automotive original equipment manufacturers (OEMs). These regional dynamics underscore a bifurcated market strategy: capacity expansion in APAC and technology leadership in North America and Europe.

Segmentation trends reveal that Multi-Gigabit PHYs (2.5G/5G/10G) are the fastest-growing segment by speed, directly addressing bottlenecks in enterprise wireless access points and small to medium-sized business (SMB) switches. By application, the Automotive Ethernet segment is exhibiting exponential growth, driven by the requirement for high-speed connectivity to support LiDAR, radar, and camera sensor fusion within vehicles, a critical enabler for autonomous driving technology. Furthermore, the increasing complexity of network design favors integrated multi-port solutions and those offering advanced diagnostics capabilities, providing end-users with better network visibility and reducing total cost of ownership (TCO).

AI Impact Analysis on Ethernet PHY Chip Market

Common user questions regarding AI's impact on the Ethernet PHY Chip Market frequently center on whether the exponential data throughput required by AI training models necessitates completely new PHY architectures, how AI workloads affect latency demands compared to traditional data transmission, and the potential for AI/Machine Learning (ML) techniques to be integrated directly into the PHY layer for better signal processing and error correction. Users are concerned about whether existing standards can scale efficiently to meet the future demands of generative AI and large language models (LLMs), which require massive, simultaneous data transfers within data center clusters. The analysis indicates a clear expectation that AI's influence is profound, primarily by driving immediate and sustained demand for ultra-high-speed, low-latency interconnects, thereby accelerating the transition to 400G and 800G Ethernet standards and pushing manufacturers towards higher levels of power efficiency per bit transferred.

The integration of AI into network infrastructure, particularly within hyperscale and cloud environments, fundamentally changes traffic patterns, shifting from typical client-server communication to east-west traffic dominated by inter-server and inter-GPU communication. This shift mandates specialized, high-density PHY chips capable of handling massive parallel data streams with minimal jitter and latency. AI inference at the edge also contributes significantly, requiring robust, low-power PHYs suitable for industrial and IoT deployment, ensuring real-time data processing and decision-making outside the traditional data center perimeter. This pressure forces innovation in SerDes (Serializer/Deserializer) technology and the adoption of advanced Digital Signal Processing (DSP) techniques within the PHY to maintain signal integrity over long channels at extreme speeds.

Furthermore, AI and ML algorithms are increasingly being utilized in the design and operation of the PHY itself. These algorithms optimize equalization and clock data recovery (CDR) circuits, allowing PHYs to dynamically adapt to varying channel conditions (temperature, cable quality) in real time, leading to improved reliability and extended reach. This internal optimization reduces bit error rates (BER) and enables manufacturers to push the limits of speed and distance using current manufacturing processes. The consensus is that AI is not just a consumer of high-speed connectivity but also a tool for enhancing the performance and efficiency of the underlying PHY technology, marking a symbiotic relationship in the evolution of modern networking components.

- AI-driven Data Center Expansion: Accelerating the deployment and adoption of 400G and 800G Ethernet PHYs for inter-server and GPU cluster communication.

- Low Latency Requirement: Mandating performance characteristics in PHY chips optimized for rapid, parallel processing of AI workloads, reducing computational bottlenecks.

- Edge AI Connectivity: Driving demand for robust, low-power industrial and automotive-grade PHYs capable of real-time data handling in non-traditional computing environments.

- PHY Design Optimization: Utilizing ML algorithms within the PHY layer for dynamic channel equalization, optimizing signal integrity, and maximizing power efficiency (pJ/bit).

- Increased Power Density: Placing extreme pressure on PHY manufacturers to reduce power consumption per port to manage overall thermal design power (TDP) in densely packed AI servers.

DRO & Impact Forces Of Ethernet PHY Chip Market

The Ethernet PHY Chip Market is predominantly driven by the continuous proliferation of digital devices and the resulting explosion in global data traffic, necessitating faster and more reliable physical layer connectivity across all network tiers. Major drivers include the global rollout of 5G infrastructure, which demands high-speed aggregation and backhaul networking equipment, and the massive, ongoing investment in hyperscale cloud data centers that require high-density, multi-rate Ethernet solutions (up to 800G). Additionally, the transition to software-defined networking (SDN) and Network Functions Virtualization (NFV) requires the underlying hardware, including PHY chips, to be highly adaptable and programmable, encouraging innovation in feature integration. These drivers create a compelling and non-negotiable need for continuous performance scaling and efficiency improvements in the physical layer.

However, the market faces significant restraints, chiefly stemming from the increasing complexity and high cost of designing and manufacturing next-generation PHY chips at advanced process nodes (e.g., 5nm or 3nm), which demands substantial research and development (R&D) investment and results in elevated product costs. Furthermore, maintaining signal integrity at extremely high data rates over increasing distances poses formidable technical challenges, often requiring sophisticated Digital Signal Processing (DSP) and complex equalization techniques that increase power consumption, counteracting efficiency goals. Supply chain volatility, especially concerning semiconductor fabrication capacity and geopolitical trade tensions, remains a persistent operational restraint that can hinder large-scale deployment and delay product launches across key application segments.

Opportunities for growth are abundant, particularly in emerging segments such as Automotive Ethernet (e.g., 10BASE-T1S, 100BASE-T1, Multi-GigBASE-T1) driven by autonomous vehicle development, and Industrial Ethernet (e.g., Single Pair Ethernet - SPE), which promises standardized connectivity for factory automation and building management systems. Furthermore, the integration of advanced diagnostic features (like Time-Domain Reflectometry or TDR) into PHY chips creates added value by enabling proactive network health monitoring and rapid fault isolation, improving overall network uptime. The increasing market adoption of Power over Ethernet (PoE) standards (PoE++, 90W) also presents opportunities for manufacturers who can integrate robust, high-power handling capabilities into their PHY designs. The primary impact forces are thus dominated by the accelerating data demands, stringent power efficiency requirements, and the technological barrier of achieving reliable high-speed SerDes performance.

Segmentation Analysis

The Ethernet PHY Chip Market segmentation provides a granular view of distinct market dynamics based on speed, application, and form factor, reflecting the diverse requirements of the end-user ecosystem. The analysis highlights the growing chasm between legacy connectivity solutions (10/100 Mbps, predominantly used in entry-level IoT and basic consumer devices) and the burgeoning high-speed segments (Gigabit and Multi-Gigabit/Higher Speeds), which are critical for enterprise infrastructure, cloud computing, and advanced industrial systems. Understanding these segments is vital for manufacturers to align their R&D efforts and capacity planning with the specific performance, power, and environmental robustness requirements of each end market, such as the low-latency needs of data centers versus the extended temperature range requirements of industrial automation.

Segmentation by application reveals that while data centers remain the largest volume consumer, the fastest growth is observed in specialized, performance-intensive areas like Automotive Ethernet, where the unique requirements for electromagnetic compatibility (EMC), fault tolerance, and reduced wiring harness weight drive premium pricing and specialized chip design. Industrial IoT and infrastructure are also experiencing rapid adoption of robust, ruggedized PHY chips designed to withstand harsh operating conditions and support long-distance transmission over copper or single-pair configurations (SPE). This bifurcation necessitates tailored product portfolios, moving away from a one-size-fits-all approach towards application-specific integrated circuits (ASICs).

Further analysis of speed-based segmentation underscores the immediate transition toward multi-gigabit speeds, particularly 2.5G and 5G, serving as intermediate solutions to address the bandwidth demands of Wi-Fi 6/6E access points without the significant power and heat penalties associated with 10G or higher solutions. The development of ultra-high-speed PHYs (100G, 200G, 400G, 800G) continues to be the domain of major data center interconnects and core network backbone infrastructure, representing the peak of technological complexity and highest revenue per unit, although lower in volume compared to enterprise or consumer-grade components. The market structure, therefore, is characterized by high-volume, low-margin legacy products coexisting with lower-volume, high-margin, technologically advanced solutions.

- By Speed Grade:

- 10/100 Mbps PHYs (Legacy and Basic IoT)

- Gigabit Ethernet PHYs (Standard Enterprise and Consumer)

- Multi-Gigabit Ethernet PHYs (2.5G/5G/10G) (Wireless Access Points, SMB Switches)

- Higher Speed Ethernet PHYs (25G, 50G, 100G, 200G, 400G, 800G) (Data Center and Core Networking)

- By Application:

- Data Center & Cloud Computing

- Enterprise Networking (Switches, Routers, Servers)

- Industrial IoT & Automation (Ruggedized Ethernet, SPE)

- Automotive Ethernet (ADAS, Infotainment, Zonal Architectures)

- Consumer Electronics & Home Networking

- Telecommunications Infrastructure

- By Port Type:

- Single-Port PHYs

- Multi-Port PHYs (Quad-port, Octal-port)

- By Technology:

- Copper PHYs (Twisted Pair, including BASE-T and BASE-T1)

- Fiber Optic PHYs (SFP, QSFP modules)

Value Chain Analysis For Ethernet PHY Chip Market

The value chain for the Ethernet PHY Chip Market is highly specialized and spans from core intellectual property (IP) development and semiconductor manufacturing to final system integration. Upstream analysis begins with semiconductor material providers and specialized IP vendors (e.g., SerDes IP cores, DSP libraries) who license crucial high-speed interface technology to fabless chip design houses. The design phase involves intense R&D focusing on power efficiency, advanced signal processing, and process node optimization. This is followed by manufacturing, which is highly concentrated among leading foundries (TSMC, Samsung, GlobalFoundries) that possess the advanced fabrication capabilities required for complex mixed-signal devices. The competitive advantage upstream rests on achieving the lowest power consumption and highest speed possible at a given process node, coupled with securing stable foundry capacity.

Midstream activities involve the core market players—the fabless semiconductor companies—who design, test, and market the PHY chips. Their role includes ensuring compliance with multiple Ethernet standards (IEEE 802.3 specifications) and tailoring products for specific applications (e.g., ruggedizing chips for industrial use or optimizing for automotive safety standards). The distribution channels are multifaceted: direct sales are common for large, strategic customers like hyperscale data centers and major network equipment OEMs (Cisco, Juniper, HPE), facilitating customization and technical support. Indirect distribution utilizes global or regional distributors (e.g., Arrow Electronics, Avnet) for broader market reach, particularly targeting smaller OEMs, contract manufacturers, and the consumer electronics sector, providing inventory management and localized logistics.

Downstream analysis focuses on system integrators and the end-users. System integrators embed the PHY chips into complex devices—ranging from network switches and servers to autonomous vehicle control units and factory floor controllers. The final stage is the end-user deployment across data centers, enterprise networks, automotive platforms, and industrial environments. The relationship between direct and indirect channels is critical; direct channels enable high-volume, custom ASIC sales and stronger technical collaboration crucial for bleeding-edge technologies, while indirect channels ensure the market availability of standardized components across thousands of diverse applications. The success of the downstream market relies heavily on the reliability, interoperability, and long-term supply assurance provided by the upstream PHY manufacturers.

Ethernet PHY Chip Market Potential Customers

The primary customers for Ethernet PHY chips are the major manufacturers of networking and communications equipment, encompassing entities responsible for building the global digital infrastructure. This includes hyperscale cloud service providers (CSPs) like Amazon Web Services, Microsoft Azure, and Google Cloud, who purchase vast quantities of high-speed PHYs (100G, 400G) directly or through their server/switch OEM partners to interconnect massive data center clusters. Telecommunications equipment manufacturers (e.g., Ericsson, Nokia, Huawei) represent another critical buyer segment, utilizing PHY chips in their 5G base stations, aggregation routers, and core network equipment, requiring robust and high-density multi-port solutions for backhaul traffic management.

A rapidly expanding customer base is found in the automotive sector, specifically among Tier 1 suppliers (e.g., Continental, Bosch, Aptiv) and Automotive OEMs (e.g., BMW, Ford, Tesla). These customers require specialized, highly robust PHY chips that comply with stringent automotive standards (AEC-Q100) and support the specific protocols of Automotive Ethernet (e.g., T1, T1S) essential for safety-critical applications like ADAS sensor processing and high-bandwidth zonal architectures. These chips must operate reliably under extreme temperature variations and electromagnetic interference, driving a distinct set of procurement requirements separate from enterprise networking.

Furthermore, the industrial automation and operational technology (OT) sector, comprising manufacturers of Programmable Logic Controllers (PLCs), industrial PCs, and factory networking gear (e.g., Siemens, Rockwell Automation), forms a growing segment. They seek PHY chips compliant with Industrial Ethernet protocols (Profinet, EtherNet/IP) and often favor the new Single Pair Ethernet (SPE) technology for long-distance, simplified cabling in factory and building management systems. Finally, the broad consumer electronics and peripheral market (manufacturers of PCs, laptops, Wi-Fi access points, and smart home devices) constitutes a high-volume, albeit often lower-margin, customer base, primarily utilizing Gigabit and Multi-Gigabit PHYs for ubiquitous connectivity.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | $1.85 Billion |

| Market Forecast in 2033 | $4.25 Billion |

| Growth Rate | CAGR 12.5% |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | Broadcom, Marvell Technology, Texas Instruments (TI), Microchip Technology, NXP Semiconductors, Analog Devices (ADI), Renesas Electronics, Credo Technology Group, Microsemi (acquired by Microchip), Realtek Semiconductor, Silicon Labs, Intel, Aquantia (acquired by Marvell), MaxLinear, Teralynx (acquired by Broadcom), Vitesse Semiconductor, Semtech, Mindspeed Technologies, Cortina Systems, Transphorm. |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Ethernet PHY Chip Market Key Technology Landscape

The technological landscape of the Ethernet PHY Chip market is defined by continuous innovation aimed at increasing data rates while simultaneously reducing power consumption and maintaining signal integrity across noisy channels. A core enabling technology is the advancement in SerDes (Serializer/Deserializer) architecture, which is fundamental for handling multi-gigabit and terabit speeds. Modern PHYs employ complex PAM4 (Pulse Amplitude Modulation 4-level) signaling schemes, particularly for speeds above 50G, moving beyond traditional NRZ (Non-Return-to-Zero) encoding to effectively double the bandwidth over existing interconnects. This shift necessitates the integration of powerful, low-latency Digital Signal Processing (DSP) blocks within the PHY to perform essential functions like forward error correction (FEC) and complex adaptive equalization, mitigating intersymbol interference (ISI) and crosstalk.

Energy efficiency is another critical technological focus, driven by the adoption of Energy Efficient Ethernet (EEE, or IEEE 802.3az) standards and the pervasive focus on power consumption in hyperscale data centers. Manufacturers are optimizing their designs at advanced process nodes (e.g., 7nm, 5nm) to minimize static and dynamic power draw, implementing dynamic voltage and frequency scaling (DVFS) and utilizing specialized low-power modes when traffic demands are low. In parallel, specialized solutions for industrial and automotive applications prioritize robustness; these designs incorporate advanced transient protection, extended operating temperature ranges, and highly specialized physical media attachment (PMA) sublayers to comply with strict electromagnetic compatibility (EMC) requirements, such as those defined by the OPEN Alliance for in-vehicle networking.

The integration of advanced monitoring and diagnostic tools is rapidly becoming a standard feature in high-end PHY chips. Technologies such as high-resolution Time-Domain Reflectometry (TDR), link quality monitoring (LQM), and comprehensive built-in self-test (BIST) capabilities allow network operators to diagnose cable faults and link issues without specialized external equipment. Furthermore, the burgeoning demand for Single Pair Ethernet (SPE) in industrial and automotive sectors introduces new PHY technology based on 10BASE-T1S/L, simplifying connectivity and reducing cable weight significantly. These technological leaps ensure that the Ethernet physical layer remains the standard bearer for reliable, high-speed wired connectivity across all critical segments of the global digital infrastructure, continually scaling to meet evolving data throughput requirements.

Regional Highlights

Global demand for Ethernet PHY chips is highly concentrated across three major regions—North America, Asia Pacific (APAC), and Europe—each contributing distinct market dynamics driven by regional economic priorities and technological adoption rates. North America stands out as the primary early adopter and key innovation center, largely owing to the presence of major hyperscale cloud service providers (CSPs) and leading technology companies. This region leads in the deployment of ultra-high-speed Ethernet (400G and 800G) within data center interconnects and core routing infrastructure, positioning it as the market segment driving the highest revenue per unit due to the complexity and high performance of the chips required for these applications. The strategic importance of minimizing latency for financial services and maximizing throughput for AI/ML workloads sustains vigorous investment in cutting-edge PHY technology.

The Asia Pacific (APAC) region dominates the market in terms of volume consumption and manufacturing output. This robust demand is propelled by two major factors: the world's highest concentration of semiconductor manufacturing facilities and the enormous consumer electronics base coupled with rapid infrastructure deployment. Countries like China, Taiwan, South Korea, and Japan are heavily investing in 5G rollouts, industrial IoT modernization, and smart city initiatives, all of which require a massive influx of Gigabit and Multi-Gigabit PHY chips. Furthermore, APAC is becoming a major force in automotive manufacturing, increasing the regional demand for specialized Automotive Ethernet PHYs as local OEMs accelerate the integration of ADAS features into their vehicle platforms. The region’s competitive manufacturing environment makes it central to the global supply chain, influencing component pricing and availability worldwide.

Europe demonstrates steady, strong growth, particularly driven by its highly regulated industrial automation and automotive sectors. The region has been proactive in adopting Industrial Ethernet standards and is a global leader in the implementation of Single Pair Ethernet (SPE) for smart factories and building control systems, seeking to standardize connectivity and reduce cabling complexity. Furthermore, European automotive manufacturers are key drivers in mandating the use of robust, high-performance Automotive Ethernet for vehicle architectures. The European market, therefore, prioritizes reliability, standardization, and compliance with rigorous safety and environmental mandates (such as strict adherence to Energy Efficient Ethernet), making it a significant market for specialized, high-quality, and robust Ethernet PHY solutions tailored for long-term operational performance in challenging environments.

- North America: Focus on hyperscale data center buildouts (400G/800G adoption), leading technology R&D, and substantial spending on enterprise networking upgrades fueled by cloud migration.

- Asia Pacific (APAC): Largest volume market; driven by 5G infrastructure development, massive industrial IoT deployment in manufacturing, and dominant global position in semiconductor fabrication and assembly.

- Europe: High adoption of Industrial Ethernet (SPE) and strict requirements for Automotive Ethernet standards (T1), emphasizing ruggedness, standardization, and energy efficiency across industrial and transportation sectors.

- Latin America and Middle East & Africa (MEA): Emerging markets showing strong adoption of Gigabit and 10G PHYs, primarily driven by regional telecom infrastructure upgrades, local data center expansion, and smart city initiatives.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Ethernet PHY Chip Market.- Broadcom

- Marvell Technology

- Texas Instruments (TI)

- Microchip Technology

- NXP Semiconductors

- Analog Devices (ADI)

- Renesas Electronics

- Credo Technology Group

- Microsemi (acquired by Microchip)

- Realtek Semiconductor

- Silicon Labs

- Intel

- MaxLinear

- Semtech

- Teralynx (acquired by Broadcom)

- Mindspeed Technologies

- Aquantia (acquired by Marvell)

- Vitesse Semiconductor

- Atheros (acquired by Qualcomm)

- Qualcomm Technologies

Frequently Asked Questions

Analyze common user questions about the Ethernet PHY Chip market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is the primary factor driving the current demand for Multi-Gigabit Ethernet PHY chips?

The primary driver is the pervasive adoption of high-performance wireless access points (Wi-Fi 6 and Wi-Fi 6E), which generate network traffic exceeding traditional Gigabit limits, necessitating 2.5G and 5G PHY chips in switches and supporting infrastructure to eliminate network bottlenecks efficiently and cost-effectively.

How is Automotive Ethernet influencing PHY chip design?

Automotive Ethernet is necessitating specialized PHY designs that meet stringent AEC-Q100 standards, featuring extended temperature ranges, enhanced electromagnetic compatibility (EMC), and reliable operation with single-pair cabling (BASE-T1), crucial for high-speed sensor data aggregation in ADAS and autonomous vehicles.

What is the significance of Single Pair Ethernet (SPE) in the Industrial IoT sector?

SPE (10BASE-T1L/S) is significant because it allows for the transmission of data and power over a single pair of wires up to 1,000 meters, dramatically reducing cabling complexity, weight, and installation costs, thereby enabling standardized, simplified connectivity across massive industrial automation and building management systems.

What are the main technical challenges in developing 400G and 800G Ethernet PHYs?

The main challenges involve managing signal integrity and insertion loss over standard channels at ultra-high speeds, requiring complex PAM4 signaling, advanced Digital Signal Processing (DSP) techniques, and aggressive power consumption minimization to keep the total power envelope of high-density switching systems feasible.

Which geographic region currently dominates the manufacturing and volume consumption of Ethernet PHY chips?

The Asia Pacific (APAC) region currently dominates both the manufacturing output and the volume consumption of Ethernet PHY chips, driven by substantial investment in 5G infrastructure, the large consumer electronics market, and the concentration of major semiconductor fabrication facilities.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager