Heterogeneous Integration Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 435108 | Date : Dec, 2025 | Pages : 255 | Region : Global | Publisher : MRU

Heterogeneous Integration Market Size

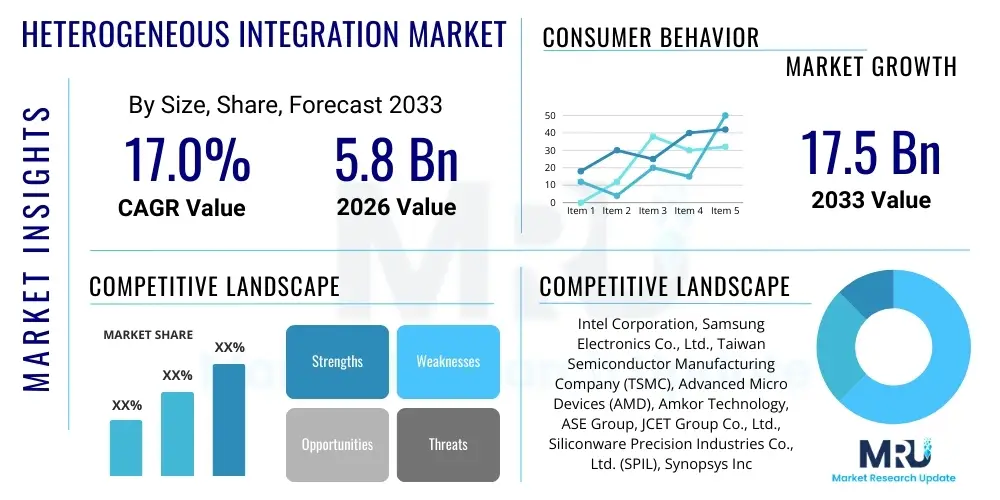

The Heterogeneous Integration Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 17.0% between 2026 and 2033. The market is estimated at USD 5.8 Billion in 2026 and is projected to reach USD 17.5 Billion by the end of the forecast period in 2033.

Heterogeneous Integration Market introduction

Heterogeneous Integration (HI) represents a transformative approach in semiconductor manufacturing, moving beyond the limitations of Moore's Law by integrating separately manufactured components—such as microprocessors, memories, sensors, and passive devices—onto a single package or system. This methodology leverages advanced packaging technologies, including 2.5D interposers, 3D stacked integrated circuits (3D-ICs), and system-in-package (SiP) solutions, to enhance functionality, improve performance, reduce power consumption, and minimize the physical footprint of electronic systems. HI is crucial for developing high-performance computing (HPC) and specialized accelerators required for modern data centers and edge computing environments.

The primary driver for the adoption of heterogeneous integration is the escalating demand for high-bandwidth, low-latency, and power-efficient semiconductor solutions across various critical applications. Products enabled by HI span diverse sectors, including high-end consumer electronics (smartphones, gaming consoles), networking and telecommunications equipment (5G infrastructure, optical transceivers), and particularly the booming fields of artificial intelligence (AI) and machine learning (ML) accelerators. By allowing chip designers to utilize the most appropriate process technology for each specific component (e.g., highly optimized logic, high-density memory, or high-power RF), HI maximizes overall system efficiency that monolithic integration often struggles to achieve.

Furthermore, heterogeneous integration facilitates the rise of the chiplet ecosystem, where standardized, functionally complete silicon blocks (chiplets) from different vendors can be combined flexibly. This shift enables greater design modularity, faster time-to- market, and significantly reduces the cost and complexity associated with designing massive system-on-chips (SoCs). The technological benefits, coupled with strong industry collaboration on standards like the UCIe (Universal Chiplet Interconnect Express), solidify heterogeneous integration's position as the foundational technology for next-generation electronic systems, offering a viable path forward for sustained performance scaling.

Heterogeneous Integration Market Executive Summary

The Heterogeneous Integration market is experiencing exponential growth, primarily fueled by the indispensable need for superior performance in AI/ML hardware, high-performance computing, and the proliferation of 5G infrastructure globally. Business trends indicate a massive capital expenditure increase in advanced packaging facilities by both Integrated Device Manufacturers (IDMs) and Outsourced Semiconductor Assembly and Test (OSAT) providers, focusing on technologies like fan-out wafer-level packaging (FO-WLP) and silicon interposers. The market structure is shifting towards collaborative models, where specialized IP providers, foundries, and advanced packaging houses form tighter partnerships to overcome yield challenges and accelerate standardization efforts, thus promoting a robust chiplet ecosystem.

Regionally, Asia Pacific (APAC) dominates the market due to its established and expanding semiconductor manufacturing base, particularly in Taiwan, South Korea, and China, which are global hubs for OSAT services and foundry operations. North America, however, leads in R&D and advanced application development, particularly in AI accelerators and high-end server processors, driven by major technology giants (hyperscalers) demanding bespoke HI solutions. Europe is focused on HI adoption in specialized industrial and automotive electronics, emphasizing reliability and stringent safety standards, representing a significant long-term growth opportunity.

In terms of segment trends, the 2.5D/3D IC stacking segment currently holds the largest revenue share, reflecting its necessity in high-bandwidth memory (HBM) integration alongside logic chips for AI and HPC workloads. Conversely, the market is seeing rapid growth in the "Modular" approach segment, supported by new interconnect standards, offering scalability and reduced design risks. Application-wise, the Data Center and Server segment maintains the highest adoption rate due to relentless data processing needs, while the Automotive sector is projected to exhibit the fastest CAGR, driven by the shift towards autonomous driving and sophisticated in-vehicle electronics demanding functional safety and high-density integration.

AI Impact Analysis on Heterogeneous Integration Market

User inquiries regarding AI's influence on Heterogeneous Integration frequently center on how HI enables the next generation of specialized AI accelerators and whether traditional packaging methods can meet the demands of large language models (LLMs) and deep neural networks. Key themes highlight the necessity of high-bandwidth memory (HBM) integration (only feasible through HI), the thermal management challenges of dense AI chips, and the role of chiplets in scaling performance while mitigating design complexity for massive AI systems. Users seek clarity on which HI technologies (e.g., 2.5D interposers vs. sophisticated 3D stacking) will become dominant for training vs. inference hardware, and the expected cost trajectory of these complex AI packages.

- AI algorithms demand extreme parallel processing, necessitating vast integration of processing units and memory.

- Heterogeneous Integration (HI) is crucial for linking logic dies with HBM stacks, providing the essential high-bandwidth interconnect (>1 TB/s) required for LLMs.

- The thermal density generated by AI accelerators requires advanced thermal solutions inherent in sophisticated HI packages.

- AI drive standardization of chiplets, allowing hyperscalers to mix and match specialized AI IP cores (e.g., TPUs, NPUs) into custom HI packages.

- HI facilitates lower power consumption per computation, which is critical for large-scale AI data centers focused on operational efficiency.

- The shift to edge AI accelerates the demand for smaller, highly integrated, and robust HI packages for deployment in consumer devices and industrial IoT.

DRO & Impact Forces Of Heterogeneous Integration Market

The Heterogeneous Integration Market is significantly shaped by a confluence of accelerating drivers and persistent restraining factors, creating strong directional forces. The primary drivers include the physical and economic limitations of traditional monolithic scaling (the end of Dennard scaling), the explosive need for specialized, high-performance computing solutions for AI/ML and 5G/6G communication, and the inherent power efficiency advantages offered by integrating optimized components. Simultaneously, the restraints are substantial, largely revolving around the increased complexity and cost associated with advanced packaging, particularly regarding thermal management, test and repair processes, and the challenges in ensuring high yield in extremely precise 3D stacking processes. These interacting forces dictate the pace of market adoption and the strategic investments required across the semiconductor ecosystem.

Opportunities in the HI market are centered on developing the chiplet ecosystem and expanding applications into non-traditional segments. The standardization efforts surrounding interconnects (like UCIe) promise to unlock immense flexibility and lower entry barriers for smaller specialized IP providers, broadening the supply base and fostering innovation. Furthermore, the migration of mission-critical systems in the automotive industry (e.g., LiDAR processing, domain controllers) from traditional PCBs to highly integrated HI modules represents a high-value opportunity, provided stringent reliability and quality standards are met. The impact forces are generally high, pushing the industry toward greater vertical collaboration between design, foundry, and packaging partners to mitigate manufacturing risks and capitalize on performance gains.

The persistent challenge of standardization across diverse advanced packaging techniques and materials remains a key restraining force, slowing down mass adoption outside of high-end niches like HPC. However, the performance demands imposed by cutting-edge technologies—specifically the necessity to integrate photonics alongside silicon for optical computing and high-speed networking—act as an unyielding driver. This mandates continuous innovation in advanced packaging materials and process flows (e.g., hybrid bonding), ensuring the market continues its upward trajectory despite the high R&D investment required. Ultimately, the market trajectory is defined by the industry's ability to consistently deliver predictable yield and reliability at scale for these complex integrated systems.

Segmentation Analysis

The Heterogeneous Integration market segmentation provides a granular view of the various technologies, components, and applications driving growth across different end-use sectors. The core segmentation relies heavily on the packaging technology employed, differentiating between 2D, 2.5D, and 3D integration techniques, which reflect varying levels of complexity, density, and performance capability. Component segmentation highlights the specific silicon elements being integrated, such as logic, memory, or mixed-signal devices. Understanding these segments is critical as market participants—from OSATs to IDMs—focus their investment and R&D efforts on specific integration platforms best suited for high-growth areas like specialized AI accelerators and high-density mobile processors. Application segmentation reveals where the highest value proposition lies, confirming the dominance of data center and enterprise computing, followed closely by the rapidly evolving automotive electronics market.

- By Technology:

- 2.5D Integration (Silicon Interposer, Organic Interposer)

- 3D Integration (Through-Silicon Vias (TSVs), Hybrid Bonding)

- Advanced 2D Integration (Fan-Out Wafer-Level Packaging (FO-WLP))

- Monolithic Integration (Wafer-to-Wafer Bonding)

- By Application:

- High-Performance Computing (HPC) and Data Centers

- Artificial Intelligence (AI) and Machine Learning (ML) Accelerators

- 5G/6G Communications and Networking

- Automotive Electronics (ADAS, Infotainment)

- Consumer Electronics (High-End Mobile Devices, Wearables)

- Industrial and Medical Electronics

- By Component:

- Logic Dies (CPUs, GPUs, FPGAs)

- Memory (HBM, LPDDR)

- Mixed-Signal ICs and Sensors

- RF and Analog Devices

- Optoelectronics

- By End-User Industry:

- IT and Telecommunications

- Automotive

- Aerospace and Defense

- Healthcare

- Industrial Automation

Value Chain Analysis For Heterogeneous Integration Market

The Heterogeneous Integration value chain is intricate, involving highly specialized activities that extend beyond traditional semiconductor manufacturing. The upstream segment is dominated by Electronic Design Automation (EDA) tool providers, IP core developers (including chiplet providers), and specialized substrate/material suppliers (e.g., TSV materials, advanced mold compounds). Design optimization for HI is uniquely complex, requiring co-design capabilities that simultaneously manage thermal performance, signal integrity, and package yield across disparate dies. The stringent requirements for reliability in HI demand highly advanced material science inputs and specialized lithography equipment tailored for packaging processes rather than pure wafer fabrication.

The core manufacturing and integration phase involves both Integrated Device Manufacturers (IDMs) like Intel and Samsung, and pure-play Outsourced Semiconductor Assembly and Test (OSAT) companies like ASE and Amkor. OSATs play a critical role, providing the necessary infrastructure for 2.5D interposers, 3D stacking via TSVs, and subsequent final testing. Distribution channels are primarily direct for high-volume, custom solutions, where major end-users (hyperscalers, automotive Tier 1s) collaborate directly with foundries or OSATs to ensure highly specific packaging requirements are met. Indirect channels are more relevant for standardized chiplet products or lower-volume HI modules sold through technology distributors.

The downstream segment includes system integrators and final product manufacturers across various industries. For instance, automotive OEMs and Tier 1 suppliers act as critical downstream customers, demanding guaranteed long-term supply and extreme reliability for HI modules used in ADAS. The feedback loop between the downstream end-users and the upstream design phase is crucial, particularly concerning packaging thermal limits and real-world performance metrics. The complexity and specialization involved mean the value chain is increasingly compressed and vertically integrated, with major players often seeking to control both the silicon manufacturing and the advanced packaging steps to ensure optimal yield and cost control.

Heterogeneous Integration Market Potential Customers

The potential customers for Heterogeneous Integration solutions are highly concentrated in sectors driven by extreme data processing needs, miniaturization, and high-speed communication requirements. The largest segment of buyers consists of massive cloud service providers and data center operators (hyperscalers) who require custom-designed AI accelerators and high-density server CPUs/GPUs to handle unprecedented volumes of data for AI training, machine learning inference, and high-performance simulation. These customers demand the highest bandwidth and lowest latency achievable, making 2.5D and 3D HI mandatory for their bespoke silicon needs.

Another major segment includes telecommunication infrastructure providers and equipment manufacturers, particularly those deploying 5G and future 6G networks. They require compact, highly integrated radio frequency (RF) and baseband processing modules that utilize HI to combine diverse materials (e.g., GaAs, SiGe) with digital logic for optimal performance in massive MIMO arrays and small cell deployment. Furthermore, the automotive sector, driven by autonomous vehicle development, is rapidly becoming a high-priority customer base. Tier 1 suppliers and OEMs need robust, fault-tolerant domain controllers and sensor fusion processors, which rely on HI for integrating powerful logic, memory, and safety monitoring elements into compact, reliable packages suitable for harsh operating environments.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | USD 5.8 Billion |

| Market Forecast in 2033 | USD 17.5 Billion |

| Growth Rate | 17.0% CAGR |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | Intel Corporation, Samsung Electronics Co., Ltd., Taiwan Semiconductor Manufacturing Company (TSMC), Advanced Micro Devices (AMD), Amkor Technology, ASE Group, JCET Group Co., Ltd., Siliconware Precision Industries Co., Ltd. (SPIL), Synopsys Inc., Cadence Design Systems, Inc., Micron Technology, Inc., SK Hynix Inc., Broadcom Inc., NVIDIA Corporation, Texas Instruments Inc., Qualcomm Technologies, Inc., GlobalFoundries Inc., IBM Corporation, Fujitsu Limited, Deca Technologies. |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Heterogeneous Integration Market Key Technology Landscape

The technological landscape of Heterogeneous Integration is rapidly evolving, driven by the shift from wire bonding and flip-chip techniques towards high-density interconnect solutions. Key technologies include 2.5D integration, which utilizes a silicon or organic interposer as a passive foundation to connect multiple dies (e.g., CPU and HBM stacks) with high-density micro-bumps, offering a balance between performance, manufacturability, and cost compared to full 3D stacking. This interposer-based approach is currently dominant in high-performance GPU and AI accelerator markets due to its proven track record in supporting very high I/O counts and bandwidth requirements.

The next frontier is 3D integration, primarily realized through Through-Silicon Vias (TSVs) and advanced processes like hybrid bonding. TSVs enable vertical connections between stacked dies, dramatically shortening interconnect lengths, thus reducing power consumption and latency. Hybrid bonding, a highly precise, low-temperature bonding technique that connects wafers or dies directly via copper pads, represents the cutting edge. It allows for ultra-fine pitch interconnects (sub-micron), enabling true 3D stacking of logic and memory layers (e.g., CMOS image sensors and memory) at densities far exceeding those possible with micro-bumps, paving the way for compute-in-memory architectures and ultimate miniaturization.

Furthermore, Fan-Out Wafer-Level Packaging (FO-WLP) is gaining traction, particularly for mobile and mid-range applications, as it eliminates the need for a traditional substrate by re-distributing connections directly on a mold compound. This offers thinner packages and better thermal performance than traditional BGA packages. Crucially, the interoperability standards, spearheaded by technologies like UCIe, are unifying the silicon ecosystem. UCIe provides a common interface specification for connecting chiplets, accelerating the adoption of heterogeneous designs by reducing integration risk and promoting multi-vendor sourcing for specialized IP blocks.

Regional Highlights

- Asia Pacific (APAC): APAC commands the largest share of the Heterogeneous Integration market, largely due to its unparalleled presence in semiconductor manufacturing, particularly in the OSAT sector (Outsourced Semiconductor Assembly and Test). Countries like Taiwan (TSMC, ASE), South Korea (Samsung, SK Hynix), and China are massive investors in advanced packaging capabilities (2.5D and 3D stacking). The strong governmental support and established supply chain infrastructure make APAC the primary execution hub for global HI production, especially for consumer electronics and memory integration.

- North America: North America is a critical region driving the market in terms of innovation, design, and high-value consumption. Dominated by major technology innovators (Intel, AMD, NVIDIA, hyperscalers), the region leads the adoption of HI for cutting-edge AI, HPC, and data center applications. Significant R&D investment, particularly in chiplet design and high-end packaging standards, positions North America at the forefront of technological advancement, even though manufacturing is heavily outsourced to APAC.

- Europe: The European market for Heterogeneous Integration is characterized by specialized application niches, particularly in the automotive, industrial control, and aerospace sectors. Strict regulatory requirements for reliability and safety mandate highly robust HI solutions. While smaller in volume compared to APAC or North America, Europe focuses heavily on integrating sensing technologies, power electronics, and high-performance computation required for advanced industrial automation and autonomous vehicle systems, fostering growth in specific high-margin segments.

- Latin America, Middle East, and Africa (LAMEA): This region is an emerging market for HI, primarily acting as a consumer of packaged devices rather than a manufacturing or design hub. Adoption is concentrated in telecommunications infrastructure upgrades (5G deployment) and localized data center expansion. Growth is dependent on global investment patterns and the rate of digitalization across these economies, showing potential for future growth as local IT infrastructure matures.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Heterogeneous Integration Market.- Intel Corporation

- Samsung Electronics Co., Ltd.

- Taiwan Semiconductor Manufacturing Company (TSMC)

- Advanced Micro Devices (AMD)

- Amkor Technology

- ASE Group

- JCET Group Co., Ltd.

- Siliconware Precision Industries Co., Ltd. (SPIL)

- Synopsys Inc.

- Cadence Design Systems, Inc.

- Micron Technology, Inc.

- SK Hynix Inc.

- Broadcom Inc.

- NVIDIA Corporation

- Texas Instruments Inc.

- Qualcomm Technologies, Inc.

- GlobalFoundries Inc.

- IBM Corporation

- Fujitsu Limited

- Deca Technologies

- Evatec AG

- Lam Research Corporation

- Applied Materials, Inc.

Frequently Asked Questions

Analyze common user questions about the Heterogeneous Integration market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is the primary technical advantage of Heterogeneous Integration over monolithic System-on-Chips (SoCs)?

The primary advantage is the ability to integrate diverse components, manufactured using optimal process nodes for their specific function (e.g., 5nm for logic, mature nodes for analog/RF, specialized processes for memory), onto a single package. This maximizes overall system performance, energy efficiency, and yield, overcoming the economic and physical constraints associated with scaling a massive monolithic SoC entirely on the most advanced process node.

How does the chiplet ecosystem relate to the growth of the Heterogeneous Integration market?

Chiplets are modular, standardized silicon blocks that are the core building material for HI. The chiplet ecosystem drives HI growth by promoting reusability, reducing design cycle times, and enabling specialized components from different vendors (like memory, logic, I/O) to be combined easily via common interconnect standards (e.g., UCIe). This flexibility accelerates the customization and deployment of high-performance devices, particularly for AI and HPC.

Which Heterogeneous Integration technology is critical for high-bandwidth memory (HBM) integration?

2.5D integration, specifically utilizing silicon or organic interposers with Through-Silicon Vias (TSVs), is the critical technology for integrating HBM with high-performance logic dies (CPUs/GPUs). The interposer provides the necessary high-density, high-bandwidth communication pathways required for HBM stacks to operate efficiently alongside the main processor, a fundamental requirement for modern AI accelerators.

What major challenges restrict the widespread adoption of 3D stacked ICs?

The major challenges include significant manufacturing complexity and cost, particularly related to the high precision required for hybrid bonding and aligning dies. Yield management is highly complex because an issue in any stacked layer can render the entire stack defective. Furthermore, efficient thermal management of vertically stacked, power-hungry dies remains a persistent engineering constraint.

In which application segment is Heterogeneous Integration expected to see the highest growth rate?

The Automotive Electronics segment, driven by the rapid development of Advanced Driver-Assistance Systems (ADAS) and autonomous vehicle technologies, is projected to exhibit the highest Compound Annual Growth Rate (CAGR). These complex systems require extremely high processing power combined with stringent functional safety and reliability standards, making highly integrated and robust HI solutions indispensable.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager