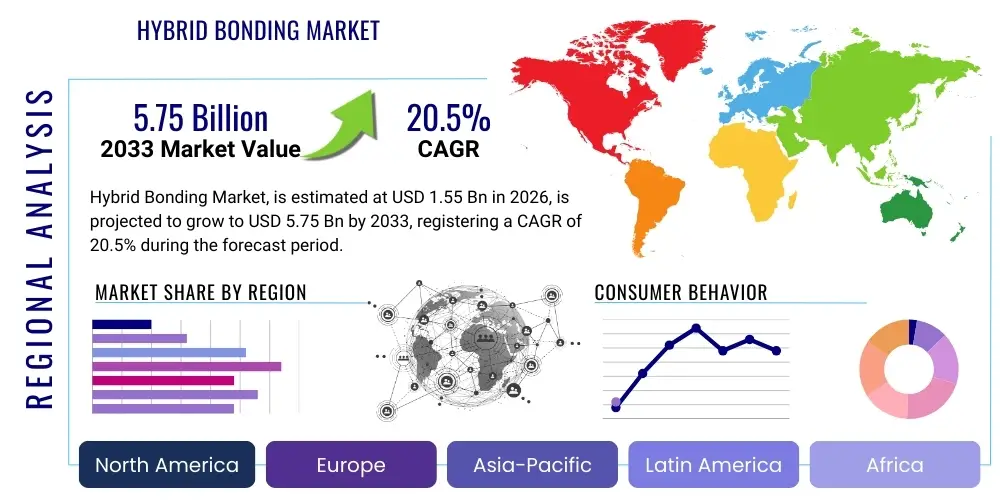

Hybrid Bonding Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 437886 | Date : Dec, 2025 | Pages : 253 | Region : Global | Publisher : MRU

Hybrid Bonding Market Size

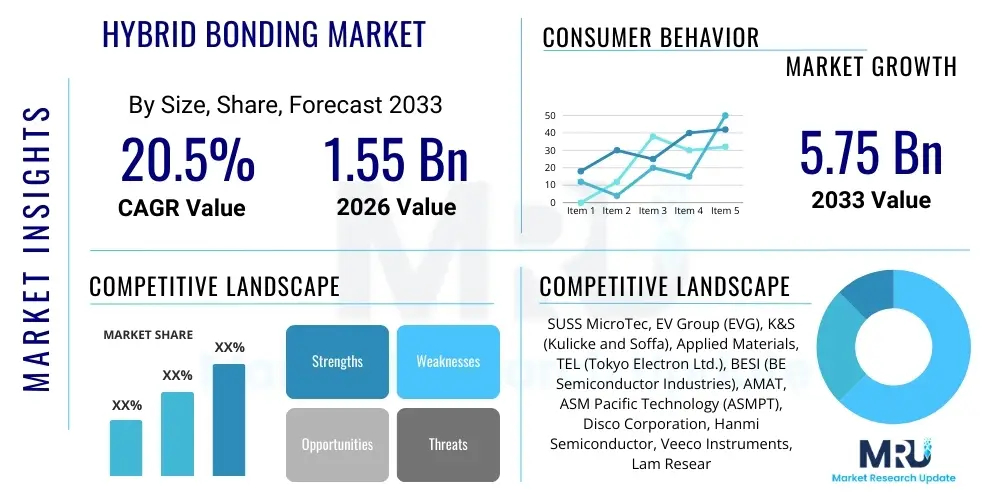

The Hybrid Bonding Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 20.5% between 2026 and 2033. The market is estimated at USD 1.55 Billion in 2026 and is projected to reach USD 5.75 Billion by the end of the forecast period in 2033.

Hybrid Bonding Market introduction

Hybrid bonding represents a revolutionary advance in semiconductor packaging, enabling ultra-fine pitch interconnection through direct metal-to-dielectric bonding. This technology facilitates the fabrication of high-density 3D integrated circuits (3D ICs) by providing superior electrical performance and mechanical robustness compared to traditional methods like micro-bumping. The process involves sophisticated surface preparation and cleaning, followed by low-temperature bonding, typically involving Cu-to-Cu or other noble metal combinations sealed by SiO₂ or similar dielectric materials. This method significantly reduces the Z-height of stacked devices, paving the way for further miniaturization and increased functionality per unit volume, which is critical for next-generation computing architectures.

The product's description centers on its capacity to establish extremely short interconnect paths, minimizing signal latency and power consumption. Major applications include advanced memory stacking, notably High Bandwidth Memory (HBM) utilized in AI accelerators and high-performance computing (HPC) systems, as well as the integration of advanced sensors such as high-resolution CMOS Image Sensors (CIS). Hybrid bonding is also foundational for implementing chiplet architectures, where disparate functional blocks are bonded side-by-side or stacked vertically to create customized systems-in-package (SiP), circumventing the limitations and costs associated with monolithic scaling.

The primary benefits of hybrid bonding are unprecedented I/O density (reaching thousands of connections per square millimeter), superior thermal dissipation capability, and enhanced system integration flexibility. Driving factors for market adoption include the relentless demand for higher data processing speeds, the proliferation of AI and Machine Learning applications requiring extreme memory bandwidth, and the technological limits encountered in traditional Moore’s Law scaling. Furthermore, the increasing complexity of heterogeneous integration across different material platforms and device types solidifies hybrid bonding's role as an indispensable enabling technology in the modern semiconductor landscape.

Hybrid Bonding Market Executive Summary

The Hybrid Bonding Market is witnessing rapid commercialization driven by substantial investments from leading semiconductor foundries and outsourced semiconductor assembly and test (OSAT) providers focusing on next-generation packaging solutions. Business trends indicate a strategic pivot toward wafer-to-wafer (W2W) bonding for high-volume, uniform integration, especially in memory and CMOS image sensors, while chip-to-wafer (C2W) bonding gains traction for heterogeneous integration and complex chiplet assembly. Key strategic alliances are forming between equipment suppliers and major integrated device manufacturers (IDMs) to standardize processes and improve yield rates, crucial for mass production scaling. The emphasis on intellectual property surrounding surface activation and alignment metrology is intensifying, reflecting the proprietary nature of high-yield hybrid bonding implementation.

Regional trends unequivocally highlight Asia Pacific (APAC) as the epicenter of hybrid bonding adoption and manufacturing capacity. This dominance is attributed to the presence of global fabrication giants, extensive semiconductor supply chain infrastructure, and robust government support for advanced packaging initiatives in countries like Taiwan, South Korea, and China. North America and Europe, while lagging in manufacturing volume, lead in research and development, particularly in advanced materials science, high-performance computing design, and specialized defense and aerospace applications that require highly customized hybrid bonded solutions. The geopolitical landscape is also subtly influencing market dynamics, pushing for localized supply chains and increased investment in advanced packaging capabilities outside traditional APAC hubs.

Segment trends confirm that the CMOS Image Sensor (CIS) segment was among the earliest and most successful adopters, utilizing hybrid bonding for improved pixel density and performance, which is essential for mobile devices and automotive cameras. However, the High-Performance Computing (HPC) and Data Center segment is projected to experience the fastest growth, primarily fueled by the indispensable requirement for High Bandwidth Memory (HBM) stacking, which fundamentally relies on hybrid bonding technology. Equipment segment growth is strong, driven by the need for ultra-high-precision aligners and dedicated surface preparation systems capable of achieving sub-micron overlay accuracy. This structural shift towards advanced packaging validates hybrid bonding as the critical enabling tool for realizing multi-functional, high-density silicon integration.

AI Impact Analysis on Hybrid Bonding Market

User queries regarding AI's impact on the Hybrid Bonding Market predominantly revolve around two core themes: first, how AI acts as a fundamental driver of demand for hybrid bonding through its need for high-density, low-latency processing hardware; and second, how AI itself can be leveraged to optimize the extremely sensitive hybrid bonding manufacturing process. Users frequently ask about the correlation between rising AI training model size and the necessity for stacked memory solutions (HBM), and they seek confirmation on whether hybrid bonding is the non-negotiable packaging technology for next-generation AI accelerators. Concerns often surface about the yield management of such complex 3D structures and the role of AI-driven metrology and inspection in maintaining the required nanoscale precision.

The synergy between AI and hybrid bonding is profound; AI serves as the primary consumption catalyst, demanding hardware (GPUs, NPUs, specialized accelerators) that cannot achieve required performance metrics without 3D integration. These systems necessitate massive parallelism and instantaneous data access, which only hybrid bonding can deliver via vertically stacked memory layers (HBM3 and beyond) integrated directly adjacent to or atop the logic die. This integration mitigates the memory wall bottleneck inherent in traditional 2D architectures, making hybrid bonding crucial for enabling the computational density required by large language models (LLMs) and advanced neural network training. The continuous scaling of AI workloads guarantees sustained high demand for hybrid bonding capacity.

Furthermore, AI is increasingly integrated into the manufacturing flow itself. The complex, multi-step nature of hybrid bonding—involving chemical mechanical planarization (CMP), ultra-clean room environments, plasma activation, and precise alignment—generates vast datasets. AI and machine learning algorithms are employed for predictive maintenance of bonding equipment, real-time process control, and advanced defect detection and classification during critical steps like surface preparation and placement. By analyzing subtle variations in process parameters and metrology data, AI drastically improves yield predictability, reduces rework time, and ensures the required high throughput and sub-micron alignment accuracy, thereby stabilizing the supply chain crucial for AI hardware production.

- AI drives demand for HBM and advanced 3D logic stacking, fundamentally relying on hybrid bonding for high bandwidth.

- Increased complexity of AI chips (e.g., large interposers, chiplets) necessitates hybrid bonding for thermal and electrical performance.

- AI algorithms are employed for predictive yield management and process optimization in highly precise bonding equipment.

- Machine learning enhances metrology and defect inspection, crucial for maintaining nanoscale alignment accuracy.

- Hybrid bonding enables heterogeneous integration, accelerating time-to-market for specialized AI accelerators (NPUs).

DRO & Impact Forces Of Hybrid Bonding Market

The market for hybrid bonding is powerfully shaped by a dynamic interplay of Drivers, Restraints, and Opportunities, collectively determining its trajectory and impact forces. Drivers primarily center on the fundamental physics and economic necessities of the semiconductor industry: the imperative for miniaturization beyond traditional lithography limits, the critical need for ultra-high memory bandwidth in computing, and the maturity of the chiplet ecosystem that relies on fine-pitch vertical integration. These forces compel foundries and packaging specialists to invest heavily in hybrid bonding capacity. The technological superiority of hybrid bonding, offering minimal electrical resistance and high I/O counts, positions it as a non-negotiable technology for achieving high-performance and power-efficient silicon solutions necessary for AI, HPC, and advanced mobile processing.

Restraints, however, pose significant technological and economic hurdles. The primary restraint is the extremely high capital investment required for hybrid bonding equipment, including ultra-precise bonders, dedicated CMP tools, and advanced metrology systems, which limits adoption primarily to Tier 1 players. Furthermore, maintaining ultra-low defectivity, especially concerning particles and surface contamination, is technically challenging, impacting production yields—a major economic barrier. Thermal management within highly stacked 3D ICs created by hybrid bonding remains a complex engineering challenge, requiring innovative cooling solutions to prevent device degradation. These restraints necessitate substantial R&D expenditure and close collaboration across the supply chain to overcome technical scaling issues.

Opportunities for the Hybrid Bonding Market are vast and strategically important. These include the expansion into non-traditional silicon platforms, such as integrated photonics for high-speed data transmission within data centers, where hybrid bonding facilitates precise alignment of silicon and compound semiconductor materials. The continued transition toward advanced automotive electronics, autonomous driving systems, and aerospace applications demanding ruggedized, high-density components represents a lucrative avenue. Additionally, the increasing acceptance of the chiplet model across the industry creates a vast addressable market for custom C2W and W2W services, enabling new entrants and specialized solution providers to capture value. The impact forces are fundamentally pushing the industry away from monolithic integration and toward heterogeneous 3D stacking, with hybrid bonding acting as the essential mechanical and electrical interface that enables this transition.

Segmentation Analysis

The Hybrid Bonding Market is segmented based on several critical criteria, including the Type of Bonding (Wafer-to-Wafer (W2W) and Chip-to-Wafer (C2W)), the End-User Application (e.g., CMOS Image Sensors, High-Performance Computing, Memory), and the Equipment and Materials used (Bonding Equipment, Metrology Tools, Chemical Mechanical Planarization (CMP) Equipment, and specialized chemical consumables). This multi-dimensional segmentation allows for a precise analysis of growth areas and strategic investment focuses within the semiconductor ecosystem. W2W bonding typically dominates volume segments due to its inherent efficiency in mass production environments, particularly for homogenous stacking like memory or image sensor integration, while C2W is gaining prominence for heterogeneous integration where different sized dies or materials are combined.

The application segment clearly illustrates market drivers, with the High-Performance Computing (HPC) category expected to exhibit the highest CAGR, primarily fueled by the exponential growth in demand for AI and deep learning accelerators requiring HBM. However, the CMOS Image Sensor (CIS) segment remains a cornerstone, having matured the technology for high-volume manufacturing earlier than other segments. Segmentation by component is equally crucial, highlighting that bonding and alignment equipment, which represents the highest initial capital outlay, is highly specialized, necessitating significant R&D from suppliers to maintain competitive edge in terms of overlay accuracy and throughput. The materials segment, covering the critical consumables like bonding chemicals and specialized planarization slurries, ensures the required surface quality for successful atomic-level bonding.

Understanding these segments is essential for strategic planning. For instance, companies focusing on W2W equipment must target high-volume foundry and IDM clients specializing in DRAM or CIS production, while those focusing on C2W equipment and services must cater to OSATs and specialized system integrators involved in complex, customized chiplet designs. The intersection of these segments—such as W2W used for stacking HBM (HPC application)—defines the most valuable market niches and dictates pricing power and technology roadmaps. As chiplet architectures become standard, the demand for flexible, high-precision C2W bonding solutions will increasingly challenge the traditional dominance of W2W, driving diversification across the supplier landscape.

- By Type of Bonding:

- Wafer-to-Wafer (W2W) Hybrid Bonding

- Chip-to-Wafer (C2W) Hybrid Bonding

- By Application:

- CMOS Image Sensors (CIS)

- High-Performance Computing (HPC) and Data Centers (including AI Accelerators)

- Memory Devices (DRAM, 3D NAND, HBM)

- Microelectromechanical Systems (MEMS) and Sensors

- Advanced Mobile Devices

- By Component/Offering:

- Equipment (Bonding Tools, CMP Systems, Inspection Systems)

- Materials and Substrates (Bonding Interconnect Materials, Dielectric Materials)

- Services (Foundry and Assembly Services)

Value Chain Analysis For Hybrid Bonding Market

The value chain for the Hybrid Bonding Market is highly specialized and encompasses distinct stages, starting from upstream suppliers of critical equipment and materials, extending through midstream fabrication and assembly services, and culminating in downstream integration by system companies. Upstream analysis focuses heavily on the providers of high-precision bonding equipment, such as permanent bonders capable of achieving sub-micron alignment and dedicated surface preparation tools like Chemical Mechanical Planarization (CMP) systems. The quality and performance of these tools directly dictate the yield and viability of the hybrid bonding process. Furthermore, chemical suppliers providing specialized slurries, etching agents, and ultra-high-purity gases are indispensable, as surface cleanliness is paramount to forming successful metallic and dielectric bonds.

The midstream segment is dominated by major foundries (IDMs) and outsourced semiconductor assembly and test (OSAT) providers who execute the complex bonding processes. Foundries, especially those involved in leading-edge logic and memory production, integrate W2W bonding in-house to maintain control over the critical stacking steps. OSATs primarily focus on C2W bonding, providing the necessary flexibility for assembling diverse chiplets and heterogeneous components. This stage involves significant investment in cleanroom infrastructure and proprietary process know-how to manage the delicate interplay between pressure, temperature, and environment required for successful hybrid integration. Process maturity and yield optimization are the primary value-added factors at this stage.

Downstream analysis involves the direct and indirect distribution channels leading to the end-users. Direct channels include the integration of hybrid bonded stacks into high-value systems by large system manufacturers—such as major technology companies developing their own AI accelerators or high-end servers. Indirect channels involve the sale of integrated components (like HBM modules or advanced CIS) through component distributors to smaller system builders in automotive, industrial, and consumer electronics markets. The complexity of the technology means that technical support and specialized consulting are often part of the distribution channel, ensuring proper integration and testing of the advanced packaged components into the final product. The tight integration required between chip design and packaging process necessitates early engagement between all value chain participants, from equipment makers to system architects.

Hybrid Bonding Market Potential Customers

The potential customer base for the Hybrid Bonding Market is diverse yet concentrated among enterprises requiring state-of-the-art semiconductor performance and density, primarily spanning integrated device manufacturers (IDMs), pure-play foundries, outsourced semiconductor assembly and test (OSAT) companies, and specific system integrators. IDMs, which design and manufacture their own components (especially memory and image sensors), are major buyers of W2W bonding equipment and materials, utilizing hybrid bonding to maintain competitive edges in product performance, such as stacking memory for GPUs or producing back-side illuminated CMOS sensors. Foundries offer hybrid bonding capabilities as a premium service to their design house clients, enabling advanced system-on-chip (SoC) architectures that utilize 3D stacking and chiplet integration.

OSAT companies constitute a rapidly growing segment of potential customers, particularly those specializing in advanced packaging services. As the industry moves towards heterogeneous integration, OSATs require flexible C2W bonding capabilities to assemble complex, multi-die packages for clients who lack internal packaging expertise or capacity. These customers serve broad markets, including automotive, industrial, and consumer electronics, demanding customization and high-mix, low-volume production capabilities, which hybrid bonding facilitates through chiplet-based designs. Their demand centers on equipment flexibility, high throughput, and cost-effective yield management across diverse material combinations and die sizes.

Beyond the direct manufacturing ecosystem, potential buyers also include system companies and hyper-scalers (e.g., Google, Amazon, Microsoft) who design their own silicon (e.g., custom TPUs or AI chips). While these companies may not perform the bonding themselves, their specifications drive the entire market, demanding the highest performance packaged solutions (like custom HBM modules) from their foundry or OSAT partners. Their continuous push for higher memory bandwidth and lower power consumption in data centers fundamentally dictates the technology roadmap for hybrid bonding applications, making them the ultimate beneficiaries and demand drivers of this specialized packaging technology.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | USD 1.55 Billion |

| Market Forecast in 2033 | USD 5.75 Billion |

| Growth Rate | 20.5% CAGR |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | SUSS MicroTec, EV Group (EVG), K&S (Kulicke and Soffa), Applied Materials, TEL (Tokyo Electron Ltd.), BESI (BE Semiconductor Industries), AMAT, ASM Pacific Technology (ASMPT), Disco Corporation, Hanmi Semiconductor, Veeco Instruments, Lam Research, Shibaura Machine, Atotech (MKS Instruments), Teradyne, PVA TePla, Brewer Science, Hitachi High-Tech, FujiFilm, Intel (as a key user and developer) |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Hybrid Bonding Market Key Technology Landscape

The technological landscape of hybrid bonding is characterized by three critical interconnected pillars: surface preparation, alignment and bonding execution, and metrology/inspection. Surface preparation is perhaps the most crucial step, involving stringent cleaning, plasma activation, and chemical mechanical planarization (CMP). CMP ensures the wafer or die surface achieves an atomic-level flatness and roughness (typically less than 0.5 nm root mean square), which is mandatory for the subsequent spontaneous covalent or metallic bond formation. Plasma activation, usually involving oxygen or nitrogen plasma, modifies the dielectric surfaces (SiO₂) to create highly reactive bonding sites, enabling low-temperature bonding below 400°C, which protects sensitive metallization layers and integrated components.

The heart of the technology lies in the bonding execution, which differentiates between wafer-to-wafer (W2W) and chip-to-wafer (C2W) processes. W2W utilizes high-precision permanent bonders capable of achieving sub-micron overlay accuracy across entire 300mm or 200mm wafers under vacuum conditions, essential for high-volume manufacturing of memory or stacked sensors. C2W, conversely, requires specialized thermo-compression bonders with advanced pick-and-place capabilities to align and place individual known good dies (KGD) onto a target wafer with equal or better precision. The advancement in C2W tooling, specifically regarding throughput and fine-pitch handling, is critical for enabling complex heterogeneous integration and accelerating the adoption of chiplet architectures across various applications.

Metrology and inspection technologies are indispensable quality control mechanisms, playing a proactive role throughout the process. Tools such as high-resolution atomic force microscopy (AFM) and scanning electron microscopy (SEM) are used to verify surface quality post-CMP and before bonding. Non-destructive testing, including advanced acoustic microscopy and infrared (IR) inspection, is necessary post-bonding to detect voids, misalignment, and potential bonding defects that could compromise the electrical or mechanical integrity of the 3D stack. Recent technological developments are focusing on integrating real-time, in-situ metrology feedback loops, often utilizing AI analysis, to automatically adjust bonding parameters and preemptively prevent yield losses, thereby driving the technology toward greater manufacturing maturity and scalability necessary for mass-market adoption in future AI systems.

Regional Highlights

Asia Pacific (APAC) stands as the undeniable leader in the Hybrid Bonding Market, largely due to its concentrated ecosystem of major semiconductor manufacturers, including TSMC, Samsung, SK Hynix, and leading OSAT providers like ASE and Amkor. The region controls the vast majority of global fabrication capacity, making it the primary site for high-volume manufacturing (HVM) applications, particularly in memory (DRAM, 3D NAND, HBM) and CMOS image sensors. Government policies in key APAC nations heavily support advanced packaging and indigenous semiconductor development, translating into massive capital expenditure on hybrid bonding equipment and infrastructure. Taiwan, South Korea, and China are particularly competitive, driving rapid technological iteration and process optimization, ensuring APAC will maintain its dominant position throughout the forecast period, especially as 3D HBM adoption accelerates in data center applications.

North America holds a pivotal role in the market, primarily as the nexus for design innovation, high-performance computing (HPC) demand, and equipment/material R&D. While fabrication volumes are lower compared to APAC, North American companies, particularly tool suppliers and specialized material providers (like those focusing on metrology or specialized adhesives), drive the cutting edge of hybrid bonding technology. Major U.S.-based technology giants are the primary consumers of highly integrated hybrid bonded components, utilizing these advanced packages in their AI accelerators and supercomputers. Furthermore, significant investments by U.S. government initiatives aimed at re-shoring semiconductor manufacturing are fueling localized capacity build-out, promising increased future market activity in advanced packaging and heterogeneous integration.

Europe contributes significantly through specialized segments, focusing on advanced materials, specialized equipment manufacturing, and high-reliability applications, such as industrial, medical, and automotive electronics. Countries like Germany and the Netherlands are home to globally leading equipment manufacturers (e.g., EV Group, SUSS MicroTec) who specialize in high-precision bonding and lithography tools, forming an essential part of the global upstream supply chain. European research institutions are heavily involved in developing hybrid integration for emerging technologies, notably integrated photonics and advanced MEMS, where hybrid bonding offers crucial assembly precision. Though smaller in scale than APAC, Europe’s focus on high-mix, high-reliability applications provides niche yet strategically important growth vectors for the overall hybrid bonding technology adoption.

- Asia Pacific (APAC): Dominates manufacturing volume, driven by leading foundries (Taiwan, South Korea) and strong demand for memory (HBM) and CIS production.

- North America: Leads in design innovation, R&D for equipment and materials, and is the primary consumer market for high-performance computing components.

- Europe: Focuses on specialized equipment manufacturing, advanced materials development, and high-reliability applications (automotive, photonics, and industrial sensors).

- Rest of the World (LATAM & MEA): Emerging market, primarily reliant on imports of packaged components, with limited fabrication activity in hybrid bonding but growing potential in specialized defense and ICT sectors.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Hybrid Bonding Market.- SUSS MicroTec SE

- EV Group (EVG)

- Kulicke and Soffa Industries (K&S)

- Applied Materials Inc. (AMAT)

- Tokyo Electron Ltd. (TEL)

- BE Semiconductor Industries N.V. (Besi)

- ASM Pacific Technology Ltd. (ASMPT)

- Disco Corporation

- Hanmi Semiconductor Co. Ltd.

- Veeco Instruments Inc.

- Lam Research Corporation

- Shibaura Machine Co., Ltd.

- Brewer Science, Inc.

- Hitachi High-Tech Corporation

- FujiFilm Holdings Corporation

- KLA Corporation

- ZEISS International

- Intel Corporation (as a developer and major end-user)

- Micron Technology, Inc.

- TSMC (Taiwan Semiconductor Manufacturing Company)

Frequently Asked Questions

Analyze common user questions about the Hybrid Bonding market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is hybrid bonding and how does it differ from traditional packaging methods?

Hybrid bonding is an advanced semiconductor packaging technology that creates extremely fine-pitch interconnections (typically sub-10 µm) by simultaneously bonding metal pads (usually copper) and surrounding dielectric materials (SiO₂) directly at low temperatures. Unlike traditional methods like micro-bumping, which use solder balls, hybrid bonding achieves permanent, robust, direct metal-to-metal and dielectric-to-dielectric contact, offering dramatically higher I/O density and superior electrical performance essential for 3D stacking.

Which applications are driving the highest demand for hybrid bonding technology?

The highest demand is driven by High-Performance Computing (HPC) and Data Center applications, particularly the need for High Bandwidth Memory (HBM). HBM stacking requires the extremely high I/O density provided by hybrid bonding to eliminate the memory wall bottleneck in AI accelerators and high-end GPUs. CMOS Image Sensors (CIS) were early adopters and remain a crucial segment, utilizing hybrid bonding for improved pixel density and integration flexibility.

What are the primary technical challenges facing the mass adoption of hybrid bonding?

The main challenges involve achieving and maintaining ultra-high alignment precision (often less than 0.5 µm overlay accuracy) and rigorously managing surface defectivity. Any particle contamination or surface roughness can lead to void formation and bond failure. Furthermore, the high capital expenditure for specialized bonding, CMP, and metrology equipment presents a significant economic barrier to widespread adoption beyond Tier 1 manufacturers.

Is Wafer-to-Wafer (W2W) or Chip-to-Wafer (C2W) bonding expected to dominate the market?

Wafer-to-Wafer (W2W) currently dominates in terms of unit volume due to its efficiency in homogenous, high-volume manufacturing (e.g., CIS and memory stacking). However, Chip-to-Wafer (C2W) is projected to experience faster growth rates, driven by the expanding adoption of heterogeneous integration and chiplet architectures. C2W offers the necessary flexibility to combine dies of different sizes, materials, and functions onto a single substrate.

How does the integration of AI affect the manufacturing process for hybrid bonding?

AI integration is crucial for optimizing yield and throughput in hybrid bonding. Machine learning algorithms are used for real-time process monitoring, predicting equipment failure, and advanced defect classification during critical steps like surface planarization and bonding alignment. By providing precise, actionable feedback on nanoscale variations, AI ensures the extremely tight tolerances required for successful 3D stack manufacturing are consistently maintained.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager