Jitter Attenuators Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 431682 | Date : Dec, 2025 | Pages : 246 | Region : Global | Publisher : MRU

Jitter Attenuators Market Size

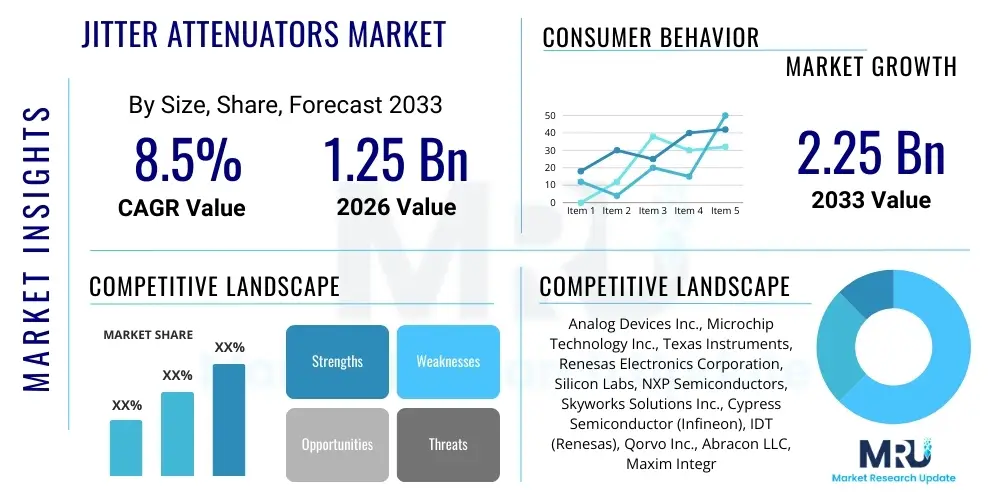

The Jitter Attenuators Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 8.5% between 2026 and 2033. The market is estimated at USD 1.25 Billion in 2026 and is projected to reach USD 2.25 Billion by the end of the forecast period in 2033.

Jitter Attenuators Market introduction

The Jitter Attenuators Market encompasses specialized electronic components designed to mitigate or significantly reduce timing errors, known as jitter, in high-speed digital communication systems and precision clocking networks. Jitter, which manifests as deviations from the ideal timing of a signal, can severely degrade system performance, increasing bit error rates (BER) and compromising data integrity. These attenuators, primarily implemented using high-performance Phase-Locked Loops (PLLs) or specialized clock clean-up circuits, are essential for ensuring reliable data transmission in modern infrastructure where high throughput and stringent timing requirements are paramount. Their fundamental function is to clean up noisy input clocks, generating a clean, stable output clock suitable for sensitive applications, thereby enabling higher data rates and improved spectral purity across various platforms.

Key applications driving the demand for jitter attenuators are concentrated in sectors experiencing rapid digitalization and infrastructure expansion. The telecommunications industry, particularly with the deployment of 5G networks and subsequent requirements for highly synchronized backhaul and fronthaul infrastructure, relies heavily on these devices to maintain precise timing across geographically distributed base stations. Similarly, massive data centers undergoing transitions to 400G and 800G Ethernet standards necessitate advanced jitter performance to manage increasingly complex serializer/deserializer (SerDes) links. Beyond communication infrastructure, other significant verticals include military and aerospace systems requiring rugged, high-reliability timing, and industrial automation where real-time synchronization is critical for deterministic control.

The primary benefits derived from integrating jitter attenuators include enhanced system performance, compliance with stringent industry standards (such as OIF, IEEE, and various Telco specifications), and reduced long-term operational costs associated with signal integrity issues. The continuous evolution towards higher modulation schemes and faster interfaces, coupled with the proliferation of edge computing requiring decentralized, accurate timing, positions jitter attenuation technology as indispensable. Driving factors for market expansion include the global push for higher bandwidth, the exponential growth of cloud services, and the necessity to manage complex clocking architectures in System-on-Chips (SoCs) and Field-Programmable Gate Arrays (FPGAs) used in high-performance computing (HPC) environments.

Jitter Attenuators Market Executive Summary

The Jitter Attenuators Market is characterized by robust business trends centered on miniaturization, integration, and the transition to ultra-low jitter performance devices capable of handling multi-gigabit data streams. Manufacturers are focused on developing highly integrated timing solutions, often combining clock generation, distribution, and jitter attenuation functionalities into single-chip solutions (Timing SoCs). This trend is driven by the need to reduce board space, power consumption, and complexity in dense systems like blade servers and 5G radio units. Furthermore, there is a pronounced shift towards specialized architectures, such as fractional-N PLLs and high-Q crystal filter-based solutions, to achieve sub-100 femtosecond RMS jitter, a requirement critical for emerging optical networking standards and high-speed analog-to-digital converters (ADCs).

Geographically, market growth is heavily skewed towards regions investing aggressively in digital infrastructure expansion. Asia Pacific (APAC) dominates the market due to massive capital expenditure in 5G rollouts, particularly in China, Japan, and South Korea, coupled with the establishment of large hyperscale data centers in emerging economies like India and Southeast Asia. North America and Europe maintain strong momentum driven by upgrades to fiber optic networks, adoption of cloud technologies, and substantial investments in aerospace and defense timing systems. Regional trends also reflect variations in compliance requirements; for instance, regulatory emphasis on network synchronization accuracy in certain European markets stimulates demand for highly compliant, carrier-grade timing devices.

Segment trends reveal that the highest growth is anticipated in devices supporting 100Gbps and 400Gbps interfaces, specifically those leveraging low phase noise characteristics. By end-user, the telecommunications segment remains the largest consumer, but the data center and enterprise networking segment is exhibiting the fastest growth rate, fueled by migration to higher data rates within short-reach interconnects. Technology segmentation highlights the increasing preference for high-performance PLL-based attenuators over traditional passive methods, given their flexibility and superior suppression of broadband and narrowband noise components. Additionally, the increasing complexity of input clock sources requires attenuators with wide frequency translation ranges and features such as automatic hitless switching and frequency margining capability.

AI Impact Analysis on Jitter Attenuators Market

Common user questions regarding AI's impact on the Jitter Attenuators Market primarily revolve around how machine learning algorithms might optimize timing stability, the demand generated by high-performance AI accelerators, and the potential for AI to aid in jitter measurement and compensation. Users are keen to understand if AI's processing demands will necessitate a new class of ultra-low jitter timing components and whether AI could be used in real-time system monitoring to predict and mitigate timing drifts. The underlying theme is the expectation that the sheer computational load of AI training and inference models in data centers and edge devices will mandate unprecedented levels of timing precision, thereby acting as a powerful accelerator for the market, particularly for high-frequency, low phase noise solutions used near sensitive serializer/deserializer interfaces and high-speed memory.

The immediate and significant impact of AI on the jitter attenuators market stems from the requirement for massive parallelism and high-speed data movement within AI clusters. AI accelerators (GPUs, TPUs, specialized ASICs) demand exceptionally clean and stable reference clocks to ensure reliable synchronization across thousands of compute cores and high-bandwidth memory interfaces (like HBM). Any residual jitter in the clock domain can translate directly into synchronization failures or data corruption at ultra-high speeds. Therefore, the implementation of advanced AI hardware necessitates top-tier jitter attenuators that can maintain picosecond or even femtosecond level precision, driving technological innovation toward integrating specialized clock clean-up functions directly onto or adjacent to AI processing units.

Furthermore, AI is indirectly influencing market dynamics through its role in predictive maintenance and system optimization. Although AI is not directly replacing the physical function of attenuation, machine learning models are being developed to analyze timing data collected from network infrastructure. These models can predict potential timing violations or drift before they impact service quality, thereby driving demand for attenuators that support robust diagnostic and monitoring features. The increasing proliferation of AI at the edge (IoT devices, autonomous vehicles) also demands highly robust and temperature-stable jitter attenuation solutions that can operate reliably in non-ideal environmental conditions, creating specialized market niches for ruggedized timing components compliant with automotive and industrial standards.

- AI accelerators require femtosecond-level clock precision, increasing demand for ultra-low jitter components.

- Increased data movement within AI/ML clusters necessitates high-performance jitter attenuation for SerDes links (400G/800G).

- AI inference at the edge drives demand for robust, temperature-stable jitter attenuators in constrained environments.

- Machine learning algorithms are employed for predictive timing maintenance, requiring attenuators with advanced diagnostic interfaces.

- AI systems push the limits of system timing complexity, favoring highly integrated timing synchronization units (TSUs) with jitter cleaning capabilities.

DRO & Impact Forces Of Jitter Attenuators Market

The Jitter Attenuators Market is governed by a dynamic set of Drivers, Restraints, and Opportunities (DRO) that shape its trajectory. The primary driving force is the relentless demand for higher bandwidth and data rates across all sectors, necessitating robust timing solutions capable of managing increasingly complex and noisy environments. This includes the global deployment of 5G infrastructure, the transition of data centers to 400G/800G optical interconnects, and the proliferation of high-speed SerDes technology in networking equipment. These advancements inherently increase system sensitivity to jitter, making high-performance attenuation essential. Furthermore, strict regulatory and standardization requirements set by bodies like ITU-T, IEEE 1588, and various telecommunications groups concerning network synchronization accuracy continuously enforce the adoption of specialized jitter cleaning devices to ensure compliance and interoperability.

Despite strong underlying demand, the market faces significant restraints. The complexity and high cost associated with manufacturing and integrating ultra-low jitter devices pose a barrier, particularly for small-scale applications or cost-sensitive consumer electronics, although these are typically not primary markets. Technical restraints include the fundamental trade-off between attenuation bandwidth and jitter cleaning capability; achieving both simultaneously requires advanced fabrication and design techniques, increasing the component's price point. Additionally, the trend toward higher integration, where timing functions are often embedded within SoCs, can sometimes limit the standalone market for discrete jitter attenuators, although this simultaneously fuels the demand for licensing highly optimized PLL IP cores. The steep learning curve required for system designers to properly characterize and manage complex timing chains also presents a technical hurdle.

Significant opportunities abound, particularly in emerging technological domains and regional expansion. The massive build-out of industrial IoT (IIoT) and smart factory infrastructure, which requires highly deterministic and synchronized control networks, presents a fertile ground for high-precision timing components. The automotive sector, driven by the shift towards autonomous driving and sophisticated in-vehicle networking (e.g., Automotive Ethernet), demands highly reliable and certified jitter attenuators. Geographically, untapped potential exists in developing economies embarking on major digital transformation projects. The development of next-generation low-power, wide-temperature-range attenuators that utilize advanced filtering techniques (e.g., MEMS resonators) also represents a core technological opportunity to differentiate products and capture specialized segments.

Segmentation Analysis

The Jitter Attenuators Market is structurally segmented based on crucial parameters including the type of device architecture (technology), the end-user application, and the required data rate supported. Analyzing these segments provides a clear view of where capital investment and technological innovation are concentrated. The core segmentation by technology differentiates between various implementations, primarily focusing on Phase-Locked Loops (PLLs) due to their superior performance in clock cleaning and frequency synthesis, compared to traditional passive filtering techniques. Within the PLL architecture, sub-segments related to the bandwidth and integration level are critical, ranging from narrow-band, high-selectivity clock cleaners used in network backbones to wide-band, integrated timing solutions utilized in high-speed processors.

End-user segmentation clearly indicates the areas of highest consumption and fastest growth. Telecommunications remains the foundational market, driven by the perpetual need for synchronization in 5G radio access networks (RAN), core networks, and optical transport. However, the data center and enterprise segment is rapidly accelerating, responding to the escalating requirements of cloud computing, virtualization, and the deployment of hyperscale facilities demanding multi-lane, synchronized SerDes links. Other influential segments, though smaller in volume, include industrial, military/aerospace, and medical electronics, where reliability and operational stability under extreme conditions often justify the deployment of premium-priced, high-specification jitter attenuators.

Further segmentation by required frequency and data rate highlights the premium commanded by devices operating in the highest frequency bands (e.g., above 10 GHz) and those supporting next-generation high-speed standards (400G and 800G Ethernet). Devices optimized for ultra-low phase noise in the sub-100 femtosecond range are increasingly critical for high-resolution RF sampling and analog-to-digital conversion, leading to premium pricing in specialized test and measurement and defense applications. This granular segmentation allows manufacturers to tailor their portfolio, addressing the distinct performance trade-offs required by different market verticals, balancing power consumption, size, cost, and ultimately, jitter performance.

- By Technology:

- PLL-based Jitter Attenuators (Fractional-N, Integer-N)

- Quartz-based (Crystal Oscillator Cleaners)

- MEMS-based Solutions

- By Frequency Range:

- Below 500 MHz

- 500 MHz to 1 GHz

- Above 1 GHz

- By End-User Application:

- Telecommunications (5G, Optical Transport, Wireless Infrastructure)

- Data Centers and Enterprise Networking

- Industrial Automation and Control

- Military and Aerospace

- Automotive

- Test and Measurement

- By Channel Density:

- Single Channel

- Multi-Channel/Integrated Clock Synthesizers

Value Chain Analysis For Jitter Attenuators Market

The value chain for the Jitter Attenuators Market is characterized by a high degree of technological specialization, starting with core intellectual property (IP) and advanced semiconductor manufacturing. The upstream segment involves the design and fabrication of complex ICs, requiring highly specialized processes (e.g., high-performance SiGe or advanced CMOS nodes) capable of achieving low noise floors and high-frequency operation. Key upstream activities include the research and development of proprietary PLL architectures, low-noise voltage-controlled oscillators (VCOs), and advanced filtering techniques. Suppliers of high-Q crystal resonators and surface acoustic wave (SAW) filters also form a critical component of the upstream ecosystem, providing the reference source required for the attenuator's operation. Profit margins in this initial stage are often protected by significant patent barriers and highly specific technical expertise.

The core manufacturing and integration stage involves major semiconductor companies that design, package, and test the jitter attenuator ICs. These manufacturers act as integrators, incorporating advanced digital control logic, high-speed analog front-ends, and robust packaging to ensure reliable performance under diverse operating conditions, particularly temperature fluctuations and vibration. Testing is a crucial, high-value step, given the stringent femtosecond-level specifications required, necessitating specialized high-frequency test equipment. The distribution channel subsequently involves specialized technical distributors (both direct and indirect) who provide localized technical support and inventory management for Original Equipment Manufacturers (OEMs) and Electronic Manufacturing Services (EMS) providers across various geographies.

The downstream analysis focuses on the integration of these devices into larger systems across diverse end-user segments. Direct sales often characterize the relationship between IC manufacturers and large, strategic customers (e.g., major telecommunication equipment providers like Ericsson or Huawei, and hyperscale data center operators). Indirect distribution, utilizing specialized channel partners, caters to smaller enterprises, regional system integrators, and the broader industrial market. The ultimate value delivery occurs when the jitter attenuator enables high-speed data integrity, adherence to network synchronization standards (e.g., PTP/IEEE 1588), and reliable operation of sensitive digital components like FPGAs and high-speed converters. The post-sales value includes ongoing technical consultation, application note support, and reference designs crucial for complex system integration.

Jitter Attenuators Market Potential Customers

The primary customers for jitter attenuators are system designers, engineers, and procurement specialists within organizations that build or manage high-speed digital communication infrastructure and precision electronic systems. The largest cohort consists of major telecommunications equipment manufacturers (TEMs) who require timing solutions for 5G base stations, optical transport networks (OTN), and core network routers and switches. These customers demand devices that meet rigorous carrier-grade synchronization standards, including support for SyncE and IEEE 1588 Precision Time Protocol (PTP), with exceptionally low phase noise floors to minimize transmission errors over long-haul fiber optics or highly congested wireless links.

A rapidly growing segment of potential customers includes operators of hyperscale and enterprise data centers, where the focus is on optimizing high-speed server interconnects and ensuring reliable operation of high-density switch fabrics. As data rates migrate from 100G to 400G and above, data center architects require jitter attenuators to clean up noisy clock inputs derived from various sources, ensuring the integrity of SerDes channels that transmit massive amounts of data between processors, memory, and network interfaces. These customers prioritize integration, low power consumption, and robustness against power supply noise, often preferring highly integrated timing modules that simplify board design and reduce component count.

Beyond the core communication sectors, crucial potential customers reside in specialized markets such as defense contractors and aerospace system integrators, who require ruggedized, radiation-tolerant jitter attenuators for radar, satellite communication, and secure military networks. Industrial automation firms and original equipment manufacturers (OEMs) of precision test and measurement instruments also represent key clientele. For instance, manufacturers of oscilloscopes, spectrum analyzers, and high-resolution medical imaging equipment rely heavily on ultra-low jitter clocks derived from attenuators to maintain measurement accuracy and signal fidelity, driving demand for the highest performance specifications available in the market.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | USD 1.25 Billion |

| Market Forecast in 2033 | USD 2.25 Billion |

| Growth Rate | 8.5% CAGR |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | Analog Devices Inc., Microchip Technology Inc., Texas Instruments, Renesas Electronics Corporation, Silicon Labs, NXP Semiconductors, Skyworks Solutions Inc., Cypress Semiconductor (Infineon), IDT (Renesas), Qorvo Inc., Abracon LLC, Maxim Integrated (Analog Devices), Integrated Device Technology, Crystek Corporation, Connor-Winfield Corporation, Fox Electronics, Linear Technology (Analog Devices), M/A-COM Technology Solutions |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Jitter Attenuators Market Key Technology Landscape

The technological landscape of the Jitter Attenuators Market is dominated by advanced Phase-Locked Loop (PLL) techniques, which are foundational to achieving high levels of noise suppression and frequency stability. Modern jitter attenuators utilize high-order PLL architectures, often employing digital loop filters and advanced delta-sigma modulation techniques to minimize quantization noise and improve output spectral purity. A crucial advancement is the transition towards integrated low-noise Voltage-Controlled Oscillators (VCOs) and Voltage-Controlled Crystal Oscillators (VCXOs) which are integrated directly into the PLL loop. This integration minimizes external noise coupling and facilitates smaller, more robust timing solutions capable of supporting multi-gigabit data rates while maintaining jitter in the femtosecond RMS range, essential for interfaces like PCIe Gen 5/6 and high-speed memory interfaces.

Beyond standard PLLs, the market is seeing increased adoption of alternative technologies to address niche requirements. MEMS (Micro-Electro-Mechanical Systems) based resonators are emerging as a promising alternative to traditional quartz crystals. MEMS timing devices offer superior resilience to shock and vibration, are significantly smaller, and exhibit better performance stability across extreme temperature ranges, making them highly attractive for industrial, automotive, and military applications. While MEMS technology historically faced challenges in achieving the lowest phase noise, continuous improvements in manufacturing and compensation techniques are rapidly closing this gap, positioning them as viable clean-up sources in demanding environments. These devices often work synergistically with PLLs to provide a highly stable, filtered reference clock input.

Another significant technological focus is on the integration of synchronization functions critical for network timing, such as support for ITU-T G.8273.2 and IEEE 1588 PTP standards. Modern jitter attenuators are evolving into comprehensive timing synchronization units (TSUs) that not only clean up noise but also manage synchronization protocols, frequency translation, and dynamic reconfiguration. This high level of integration reduces system latency and complexity, critical factors in 5G wireless backhaul and enterprise networking where deterministic time delivery is paramount. Manufacturers are leveraging advanced CMOS processes (down to 28nm or less) to integrate more digital functionality, enabling features like hitless switching between reference clocks, automatic drift compensation, and enhanced diagnostic monitoring capabilities for proactive system management.

Regional Highlights

- Asia Pacific (APAC): APAC is the epicenter of growth, driven primarily by hyper-aggressive 5G rollouts, especially in China, South Korea, and Japan, necessitating vast quantities of high-performance jitter attenuators for infrastructure synchronization. Furthermore, the region is experiencing unprecedented investment in hyperscale data centers, particularly in Southeast Asia and India, fueled by increasing cloud adoption and domestic digital consumption. Government initiatives supporting digital transformation and smart city projects also contribute significantly to the high demand for precision timing components, making it the highest revenue generating region globally and maintaining the fastest projected CAGR.

- North America: This region is characterized by early adoption of cutting-edge technology and high investment in complex systems, including aerospace, defense, and high-performance computing (HPC). Demand here is focused on ultra-low jitter devices required for advanced RF sampling and defense communications. The continuous upgrade cycles within large cloud service providers (CSPs) transitioning to 400G and 800G optical interconnects are substantial market drivers. North America leads in innovation, particularly in the development of sophisticated Timing SoCs that integrate multiple clock functions onto a single die, addressing the need for reduced complexity in advanced network architectures.

- Europe: The European market maintains stable growth, primarily driven by stringent requirements for telecommunication network resilience and synchronization, enforced by regional regulatory bodies. Key growth areas include the deployment of fiber-to-the-home (FTTH) networks and industrial automation projects (Industry 4.0), which necessitate highly reliable and deterministic timing protocols. Europe also has a strong presence in the automotive sector, where demand for certified jitter attenuators for Automotive Ethernet and advanced driver-assistance systems (ADAS) is steadily increasing.

- Latin America (LATAM): The LATAM region presents significant growth potential, albeit starting from a smaller base. Market expansion is correlated with increasing investments in broadband infrastructure modernization, particularly in Brazil and Mexico. The deployment of initial 5G networks and the establishment of local data centers by international cloud providers are key drivers stimulating the demand for basic to mid-range performance jitter attenuation solutions necessary for network build-out and modernization projects.

- Middle East and Africa (MEA): Growth in the MEA region is segmented, with high spending concentrated in the Gulf Cooperation Council (GCC) countries (UAE, Saudi Arabia) on mega-projects and smart city initiatives, demanding world-class communication infrastructure. The adoption of 5G is progressing rapidly in major economies, fueling demand for timing synchronization equipment. In Africa, market expansion is more incremental, tied to increasing mobile penetration and infrastructure projects financed by international development funds, requiring cost-effective and ruggedized timing solutions.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Jitter Attenuators Market.- Analog Devices Inc.

- Microchip Technology Inc.

- Texas Instruments

- Renesas Electronics Corporation

- Silicon Labs

- NXP Semiconductors

- Skyworks Solutions Inc.

- Qorvo Inc.

- Abracon LLC

- Crystek Corporation

- Connor-Winfield Corporation

- Fox Electronics

- Integrated Device Technology (IDT, now part of Renesas)

- Cypress Semiconductor (now part of Infineon)

- M/A-COM Technology Solutions

Frequently Asked Questions

Analyze common user questions about the Jitter Attenuators market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is the primary function of a Jitter Attenuator in high-speed systems?

The primary function of a Jitter Attenuator is to clean up a noisy input clock signal by utilizing a narrow-band Phase-Locked Loop (PLL) filter. This process suppresses timing errors (jitter) and phase noise present in the input reference, generating a clean, stable output clock essential for maintaining high data integrity and low bit error rates (BER) in high-speed digital and communication interfaces like SerDes and 5G optical links. It ensures precise synchronization across complex networks.

How is the performance of a Jitter Attenuator measured and quantified?

Performance is quantified primarily by its RMS (Root Mean Square) Jitter value, typically measured in femtoseconds (fs) or picoseconds (ps), indicating the deviation from the ideal clock edge. Other critical metrics include Phase Noise (measured in dBc/Hz), which describes noise power at specific offsets from the carrier frequency, and Jitter Transfer Function (JTF), which defines the device's ability to suppress input jitter across various frequencies.

Which end-user segment is driving the highest growth in the Jitter Attenuators Market?

The Data Centers and Enterprise Networking segment, specifically due to the shift towards hyperscale facilities and the rapid adoption of 400G/800G Ethernet standards, is exhibiting the fastest growth. These systems require complex clocking architectures and ultra-low jitter components to ensure reliable operation of high-speed optical and electrical interconnects (SerDes), surpassing current growth rates even within the established Telecommunications sector.

What are the key technical constraints facing the development of next-generation jitter attenuators?

Key technical constraints involve the fundamental trade-off between reducing power consumption and achieving ultra-low phase noise (sub-100 fs RMS jitter) in increasingly integrated solutions. Designers struggle to integrate high-Q resonators and low-noise VCOs onto standard CMOS processes without compromising spectral purity or increasing complexity. Furthermore, managing the interaction between high-frequency analog components and dense digital logic poses significant electromagnetic compatibility (EMC) challenges.

What role does the IEEE 1588 Precision Time Protocol (PTP) play in the Jitter Attenuators Market?

PTP is critical as it defines the required standard for highly accurate network synchronization. Jitter attenuators designed for PTP-compliant systems often integrate advanced digital processing to manage the PTP clock recovery algorithm, filter timing noise introduced during transmission, and ensure the local clock output adheres strictly to the required synchronization accuracy (often nanosecond-level). This integration is vital for applications like 5G base station synchronization and industrial control networks.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager