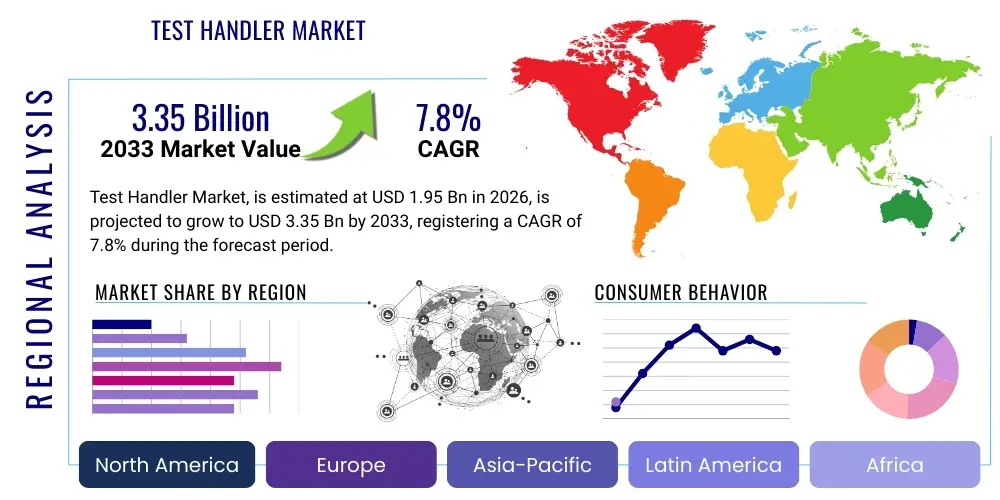

Test Handler Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 436745 | Date : Dec, 2025 | Pages : 243 | Region : Global | Publisher : MRU

Test Handler Market Size

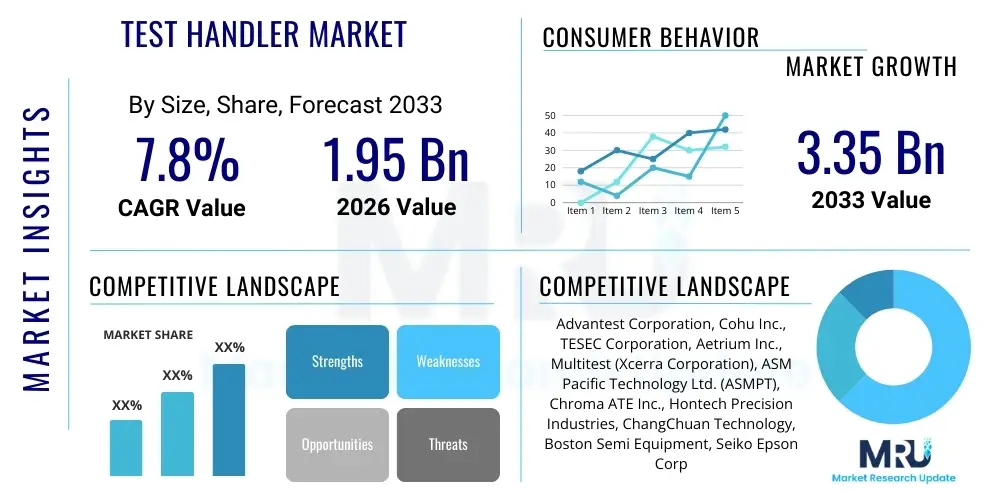

The Test Handler Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 7.8% between 2026 and 2033. The market is estimated at $1.95 Billion in 2026 and is projected to reach $3.35 Billion by the end of the forecast period in 2033. This substantial growth is fundamentally driven by the relentless expansion of the global semiconductor industry, particularly the accelerating demand for complex, high-performance integrated circuits (ICs) used in high-growth sectors such as 5G infrastructure, artificial intelligence (AI) hardware, and advanced automotive electronics.

Test Handler Market introduction

The Test Handler Market encompasses the manufacturing and supply of automated mechanical systems crucial for the semiconductor final test process. These sophisticated machines interface with Automatic Test Equipment (ATE) to physically manipulate, position, and control the temperature of semiconductor devices—ranging from microprocessors and memory chips to analog and mixed-signal components—during electrical testing. The primary function of a test handler is to ensure high throughput and reliability by automatically feeding untested devices (DUTs) into the ATE test site, removing tested devices, and sorting them based on pass/fail criteria, thereby guaranteeing quality control before chips enter the downstream supply chain. The efficacy of a test handler directly impacts the total cost of testing and the time-to-market for new semiconductor products, making handler technological advancements vital for competitive manufacturing.

Test handler products are categorized broadly by their handling mechanism, including gravity-fed handlers suitable for high-volume, standard packages; pick-and-place handlers offering high flexibility for array packages and varied device geometries; and turret handlers known for extremely high-speed, parallel testing capabilities, often utilized for memory and small logic devices. Major applications span across integrated device manufacturers (IDMs), outsourced semiconductor assembly and test (OSAT) companies, and pure-play foundries, all striving to meet stringent quality standards for high-reliability applications such as aerospace, medical implants, and mission-critical data center components. The evolution of semiconductor packaging, including chip-scale packages (CSPs), ball grid arrays (BGAs), and wafer-level packages (WLPs), continuously pushes the requirement for higher precision, faster index times, and more complex thermal management capabilities within handler systems.

Key benefits derived from advanced test handler adoption include significantly enhanced testing throughput, reduced human error through automation, and precise thermal conditioning necessary to simulate real-world operating environments during testing. Driving factors for market expansion include the global push toward greater connectivity via 5G and 6G networks, which necessitates massive production of complex radio frequency (RF) and high-speed digital chips; the aggressive adoption of electric vehicles (EVs) and autonomous driving systems requiring robust, zero-defect power management and sensor chips; and the overall densification of computing power driven by cloud infrastructure. These trends mandate continuous investment in cutting-edge test handling infrastructure capable of handling increasing complexity and parallelism in testing procedures.

Test Handler Market Executive Summary

The Test Handler Market exhibits robust growth propelled by secular business trends, particularly the unprecedented acceleration in semiconductor content across all major end-use industries, including computing, communications, automotive, and industrial IoT. Strategic investments by leading OSAT providers and IDMs into advanced automated test solutions are defining the current competitive landscape, prioritizing handlers that can manage heterogenous integration, 3D packaging, and extremely high pin counts. Current business trends indicate a strong shift towards modular and scalable handler architectures that can easily adapt to generational changes in semiconductor testing requirements without necessitating complete system replacement. Furthermore, sustainability and operational efficiency are becoming core business considerations, driving demand for handlers with lower energy consumption and enhanced mean time between failures (MTBF), thus reducing the overall total cost of ownership (TCO) for manufacturers.

Regional trends clearly position Asia Pacific (APAC), led by Taiwan, South Korea, China, and Japan, as the dominant and fastest-growing region. This supremacy is attributed to APAC being the global epicenter for semiconductor manufacturing, assembly, and testing operations (OSATs and Foundries). Government initiatives in regions like China to bolster domestic chip production further intensify the demand for localized handler solutions. North America and Europe, while slower in manufacturing capacity growth, remain crucial for high-end research and development testing and niche high-reliability applications, often driving demand for ultra-precise handlers and advanced thermal simulation capabilities, especially in defense and aerospace sectors. The intense capital expenditure cycles associated with new wafer fabrication facilities (fabs) globally serve as a leading indicator for subsequent handler market demand.

In terms of segment trends, the pick-and-place segment is experiencing significant momentum due to its versatility in handling advanced packaging formats such as SiP (System-in-Package) and fan-out wafer-level packaging (FOWLP). The application segment is heavily influenced by the digital IC and memory sub-segments, correlating directly with the massive global demand for DRAM, NAND, and AI accelerators. Moreover, there is a pronounced segment trend toward integrating sophisticated features, such as advanced vision systems for precise device alignment and high-performance temperature forcing units capable of achieving extreme temperature ranges (e.g., -55°C to 150°C), critical for comprehensive environmental stress testing (EST) of automotive and high-reliability components. This technological convergence ensures that handlers remain indispensable tools in the quality assurance pipeline.

AI Impact Analysis on Test Handler Market

User queries regarding AI's impact on the Test Handler Market primarily center on how artificial intelligence and machine learning (ML) will enhance testing efficiency, reduce unscheduled downtime, and facilitate the transition from conventional, static test programs to dynamic, adaptive testing methodologies. Common concerns relate to the immediate necessity of integrating edge computing capabilities into handler systems for real-time decision-making, alongside expectations for AI-driven fault prediction and isolation. Users are keen to understand if AI can significantly lower the current high rates of false positives or false negatives in high-speed sorting. Furthermore, interest focuses on how AI can optimize handler mechanical movement and thermal control routines, thereby maximizing throughput and minimizing physical stress on fragile, advanced semiconductor packages.

The integration of AI into the testing ecosystem is transforming test handler operations from purely mechanical automation to intelligent, predictive automation. AI algorithms are being deployed to analyze vast datasets generated during the testing process—including temperature logs, mechanical movement telemetry, and electrical test results—to identify subtle correlations indicative of potential equipment failure or process drift. This shift enables predictive maintenance, drastically reducing the risk of catastrophic downtime, which is extremely costly in high-volume semiconductor manufacturing environments. Furthermore, AI enhances test program optimization by learning optimal testing sequences and conditions, allowing the handler and ATE to work synergistically to reduce overall test time without compromising coverage, directly improving capital utilization.

The adoption of computer vision powered by deep learning is paramount in achieving micron-level precision for device handling and alignment, crucial for extremely small or irregularly shaped advanced packages. AI assists handlers in detecting minute physical defects, recognizing misalignment patterns, and compensating for wear and tear in real-time. This real-time adaptive capability means the handler can modify its operational parameters based on environmental fluctuations or device variation, ensuring consistent and reliable handling integrity throughout multi-shift operations. Ultimately, AI integration elevates the test handler from a piece of deterministic equipment to an integral component of a smart factory infrastructure, optimizing overall production yield and quality control.

- AI optimizes handler movements and mechanical routines, maximizing indexing speed and reducing physical stress on devices.

- Predictive maintenance schedules are enabled through machine learning analysis of vibration, thermal, and utilization data, minimizing unexpected downtime.

- Adaptive test flow optimization utilizes AI to dynamically select and execute the minimum necessary test steps based on prior device performance, shortening test time.

- Enhanced vision systems powered by deep learning improve precision in device alignment (critical for small pitch packages) and defect inspection.

- Real-time anomaly detection flags handler performance issues or subtle shifts in device quality, improving overall test reliability and yield.

DRO & Impact Forces Of Test Handler Market

The Test Handler Market is currently defined by powerful driving forces centered on technological complexity and application expansion, counterbalanced by significant restraints concerning capital expenditure and technological lifespan. Opportunities arise mainly from novel semiconductor architectures and emerging high-growth industries. The primary driving force is the relentless complexity increase in integrated circuits, including higher pin counts, finer pitch sizes, and advanced packaging techniques (like 2.5D/3D integration), demanding superior handler precision and complex thermal control capabilities. Restraints include the extremely high initial capital investment required for high-speed, high-performance handlers, coupled with the rapid technological obsolescence cycle inherent in the semiconductor equipment sector, forcing manufacturers into constant reinvestment. Opportunities are abundant in the growth of automotive electronics (especially power semiconductors and sensor fusion chips), high-performance computing (HPC) accelerators, and the nascent deployment of 6G communication infrastructure, all of which require specialized and highly reliable handling solutions.

Key drivers include the global proliferation of 5G and ongoing development of 6G technologies, demanding vast quantities of RF, modem, and high-speed digital chips that require rigorous high-frequency testing and complex thermal management. Secondly, the automotive industry's electrification and autonomy trends necessitate zero-defect testing for power management units (PMUs), microcontrollers, and sensor chips, boosting the need for handlers optimized for high-reliability, wide-temperature testing. The structural shift towards heterogeneous integration and advanced packaging, where multiple dissimilar chips are packaged together (e.g., SiP), requires highly flexible and precise pick-and-place handlers that can accommodate diverse package types and high parallelism. These factors create sustained long-term demand for advanced handling systems capable of parallel testing hundreds or thousands of devices simultaneously.

Conversely, significant restraints hinder market fluidity. The substantial cost of advanced test handler systems often creates a high barrier to entry for smaller OSAT players and leads to extended budget justification cycles for major corporations. Furthermore, the specialized nature of these systems necessitates ongoing maintenance and highly skilled technical personnel, contributing significantly to operational expenditures. The semiconductor industry's cyclical nature, characterized by periods of oversupply and under-utilization, can lead to sudden drops in capital equipment orders, impacting handler manufacturers. Moreover, the risk associated with developing new handlers that meet future, yet-to-be-standardized packaging technologies poses a considerable technological restraint, requiring significant R&D investment with uncertain payoff.

The resulting impact forces indicate a competitive environment focused less on mere throughput and more on system versatility, precision, and integration capabilities. Handlers offering seamless integration with factory automation systems (like MES) and enhanced data output capabilities are gaining market share. Strategic mergers, acquisitions, and partnerships between handler manufacturers and ATE providers are increasingly common, aimed at delivering optimized, unified test solutions. The market is also heavily influenced by geopolitical factors, particularly trade policies affecting the semiconductor supply chain, compelling manufacturers to diversify their sourcing and manufacturing footprints to mitigate risks associated with regional concentration, thereby influencing where capital equipment, including test handlers, is purchased and deployed.

Segmentation Analysis

The Test Handler Market is systematically segmented based on mechanism type, device application, end-user industry, and operational capabilities, reflecting the diverse and specialized requirements of the global semiconductor testing landscape. Analyzing these segments provides critical insights into market penetration and growth trajectories driven by technological shifts. The dominant segmentation by type includes gravity-fed, pick-and-place, and turret handlers, each catering to different levels of throughput, package complexity, and required thermal control. Gravity handlers remain vital for high-volume, low-cost commodity testing, whereas pick-and-place handlers are rapidly gaining prominence due to their adaptability for complex, array-based packages. Segment performance is also highly correlated with end-user concentration, with OSATs driving massive volumes in pick-and-place and gravity segments, while IDMs often invest in highly customized, specialized systems for R&D and proprietary chip production.

Segmentation by device application is crucial, dividing the market into digital, memory, analog and mixed-signal, and RF semiconductor testing. The rapid growth of data centers and consumer electronics means the digital and memory segments consume the largest portion of handler capacity. However, the automotive and industrial sectors are bolstering demand for sophisticated handlers in the analog and mixed-signal categories, requiring extremely accurate temperature forcing and low electrical noise environments to ensure precise component calibration. Furthermore, the capacity for high-parallelism testing, differentiating handlers by the number of devices tested simultaneously, is becoming a key differentiator, particularly in the memory and high-volume logic markets where manufacturers prioritize minimizing cost per test (CPT).

- By Type:

- Gravity-fed Handlers

- Pick-and-Place Handlers (Horizontal and Vertical)

- Turret Handlers

- Wafer Level Handlers

- By Device Application:

- Digital ICs (Microprocessors, ASICs)

- Memory Devices (DRAM, NAND, Flash)

- Analog and Mixed-Signal ICs

- RF Devices and Power Semiconductors

- By End User:

- Outsourced Semiconductor Assembly and Test (OSAT) Companies

- Integrated Device Manufacturers (IDMs)

- Foundries (Pure-play and IDM-Foundries)

- By Operational Capabilities:

- High-speed/High-volume Handlers

- High-temperature/Low-temperature Handlers (Thermal Forcing)

- High-Reliability/High-Precision Handlers

Value Chain Analysis For Test Handler Market

The value chain of the Test Handler Market begins with upstream suppliers providing critical, high-precision components such as advanced robotics, motion control systems, high-accuracy vision components, complex thermal management systems (chillers and hot/cold plates), and specialized materials for contactors and docking mechanisms. These upstream inputs are highly specialized and often sourced from a limited number of high-technology suppliers, making supply chain resilience a critical factor for handler manufacturers. Handler vendors must maintain deep engineering relationships with these suppliers to ensure the integration of the latest technological breakthroughs, particularly in high-speed motion control and thermal regulation, which directly impact handler performance metrics such as index time and temperature accuracy.

Downstream, the manufactured test handler systems are distributed through a combination of direct sales teams and strategic local distributors, often involving close cooperation with the end-users—OSATs, IDMs, and Foundries—to ensure customization and smooth integration into existing ATE infrastructure. The distribution channel involves significant post-sale support, including installation, calibration, and long-term maintenance contracts, as handlers are highly sensitive, complex capital equipment requiring specialized expertise. Direct sales channels are typically employed for major strategic accounts and highly customized, high-value systems, allowing for direct feedback loops between the manufacturer and the user regarding performance and necessary feature modifications. Indirect channels, often local engineering representatives, are essential for penetrating regional markets, particularly in Asia Pacific, providing local language support and rapid service response.

The final stage involves the deployment and utilization of the handler in the customer’s high-volume production environment. This step emphasizes the importance of reliable performance, minimal downtime, and continuous technical support. The relationship between the handler manufacturer and the end-user is often long-term, extending through multiple technology generations, as replacement cycles are dependent on technology refresh rates and capacity expansion plans. The efficiency gains achieved by the handler directly influence the end-user’s profitability and time-to-market, cementing the handler’s position as a crucial, non-commoditized asset in the semiconductor manufacturing value chain. The complexity of integration requires handler vendors to also work closely with ATE manufacturers to guarantee seamless interoperability and optimized test floor utilization.

Test Handler Market Potential Customers

Potential customers for test handler equipment primarily comprise entities within the semiconductor manufacturing ecosystem that perform high-volume, automated electrical testing of integrated circuits (ICs). The largest customer base is the Outsourced Semiconductor Assembly and Test (OSAT) segment, which relies heavily on advanced handlers to manage the tremendous volume and variety of chips assembled and tested for fabless companies and IDMs globally. OSAT providers prioritize handlers that offer exceptional throughput, high parallelism, and flexibility to rapidly switch between different package types (quick changeover kits) to maximize equipment utilization across diverse customer requirements. Their capital expenditure decisions are heavily weighted towards CPT reduction and operational efficiency.

Integrated Device Manufacturers (IDMs), which design, manufacture, and test their own chips, constitute another critical customer segment. IDMs often require handlers for internal quality control, specialized pre-production testing, and verification of high-value or proprietary devices. These customers typically demand handlers with ultra-precise thermal control and superior mechanical handling integrity, often customized to proprietary test protocols. Similarly, pure-play foundries, while primarily focused on wafer fabrication, increasingly engage in back-end services, including pre-packaging burn-in and functional testing, thereby becoming significant buyers of high-precision, high-throughput handling systems, particularly wafer-level test handlers.

Emerging and specialized end-users, such as large-scale automotive electronics suppliers and critical infrastructure defense contractors, represent a growing niche for handlers. These buyers require equipment capable of extreme environmental testing (wide temperature ranges, mechanical shock simulation) to ensure zero-defect reliability for safety-critical applications. Additionally, research institutions and pilot production lines focusing on next-generation materials (e.g., SiC, GaN power electronics) are potential customers seeking highly flexible, lower-volume handlers capable of supporting diverse experimentation and process development needs, marking a strategic area for specialized handler manufacturers focusing on technological advancement rather than pure volume.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | $1.95 Billion |

| Market Forecast in 2033 | $3.35 Billion |

| Growth Rate | 7.8% CAGR |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | Advantest Corporation, Cohu Inc., TESEC Corporation, Aetrium Inc., Multitest (Xcerra Corporation), ASM Pacific Technology Ltd. (ASMPT), Chroma ATE Inc., Hontech Precision Industries, ChangChuan Technology, Boston Semi Equipment, Seiko Epson Corporation, Micronics Japan Co., Ltd. (MJC), Mactech, Jupiter Semiconductor, YAMAHA Robotics. |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Test Handler Market Key Technology Landscape

The technological landscape of the Test Handler Market is rapidly evolving, driven by the demands for higher throughput, sub-micron precision, and extensive thermal control necessary for next-generation semiconductor testing. One critical technological advancement is the integration of advanced Thermal Subsystems, including high-performance temperature forcing units and localized thermal plates capable of rapid temperature transitions across extremely wide ranges (e.g., -60°C to 175°C). This capability is essential for automotive and military specifications, requiring highly reliable components tested under rigorous environmental stress. Furthermore, the development of sophisticated Contacting Solutions, such as precise vertical probe cards and specialized test sockets, is necessary to maintain signal integrity during high-speed testing (up to 100 Gbps or higher), particularly for complex interfaces like DDR5 and PCIe 6.0, demanding handlers with superior docking precision and minimal impedance disruption.

Another pivotal technology area is the utilization of advanced Robotics and Motion Control Systems. Modern handlers employ highly synchronized multi-axis robots and precision linear motors to achieve faster index times (the time taken to move one device in and out of the test site) while maintaining high positional accuracy (often below 50 microns). This is augmented by sophisticated Vision System Integration, utilizing high-resolution cameras and pattern recognition algorithms (often AI-enhanced) to ensure precise device alignment and pre-test inspection for coplanarity or damage detection, which is vital for tiny, high-density packages like CSPs and QFNs. These technologies collectively enable the high parallelism required in today's testing environment, minimizing the mechanical component of the overall test time and maximizing ATE utilization, directly addressing the core market need for lower Cost Per Test (CPT).

The increasing focus on factory automation necessitates advanced Software and Communication Interfaces. Handlers are now expected to be fully compatible with Semiconductor Equipment and Materials International (SEMI) standards, such as GEM/SECS, allowing for seamless integration with manufacturing execution systems (MES) and centralized data logging platforms. This technological push supports the shift toward Industry 4.0 principles, enabling real-time monitoring, remote diagnostics, and predictive analytics that optimize handler uptime. Finally, the development of Modular Handler Designs allows customers to quickly reconfigure systems—swapping out temperature modules, index modules, or sorting mechanisms—to adapt to varying package formats and test requirements, extending the usable life of the capital equipment and mitigating obsolescence risk, making flexibility a key technological selling point over pure speed.

Regional Highlights

The global Test Handler Market exhibits distinct regional dynamics, primarily dominated by the production and testing activities concentrated in Asia Pacific (APAC), with North America and Europe retaining significance in high-end design and specialized applications.

- Asia Pacific (APAC): APAC is the unequivocally largest and fastest-growing market for test handlers, driven by the presence of the world's leading OSAT providers (e.g., ASE, Amkor Technology, JCET) and major foundry operations (e.g., TSMC, Samsung). Countries like Taiwan, South Korea, Mainland China, and Japan represent the bulk of global semiconductor assembly and test capacity. Government initiatives promoting domestic semiconductor manufacturing, particularly in China and India, are fueling massive capital expenditure into new testing infrastructure, leading to surging demand for both high-speed, high-volume gravity feeders and versatile pick-and-place handlers suitable for diverse consumer electronics and memory components.

- North America: This region is crucial for the design and development of cutting-edge ICs, particularly in AI, HPC, and specialized aerospace/defense applications. Demand here focuses less on sheer volume and more on high-precision, low-volume handlers designed for R&D, advanced characterization, and military-grade testing. North American IDMs and fabless giants drive technological innovation in handler features, specifically demanding superior thermal accuracy and the ability to handle extremely complex or novel package architectures before they transition to mass production in APAC.

- Europe: The European market demonstrates steady demand, particularly concentrated in Germany, France, and the Nordic countries, focusing heavily on industrial, automotive, and power semiconductor testing. The strong regional presence of major automotive manufacturers and tier-one suppliers necessitates rigorous, high-reliability testing (AEC-Q100 standards), driving the need for handlers with robust temperature cycling capabilities and exceptional mechanical integrity for SiC and GaN power devices.

- Latin America, Middle East, and Africa (MEA): These regions represent emerging markets, primarily relying on imported chips and limited local assembly/test operations. Demand for test handlers is focused on localized assembly operations (often targeting regional markets) and repair/refurbishment facilities. While smaller in volume, these regions present opportunities for entry-level, reliable handler systems with localized service support as regional electronics manufacturing expands.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Test Handler Market.- Advantest Corporation

- Cohu Inc.

- TESEC Corporation

- Aetrium Inc.

- Multitest (Xcerra Corporation)

- ASM Pacific Technology Ltd. (ASMPT)

- Chroma ATE Inc.

- Hontech Precision Industries

- ChangChuan Technology

- Boston Semi Equipment

- Seiko Epson Corporation

- Micronics Japan Co., Ltd. (MJC)

- Mactech

- Jupiter Semiconductor

- YAMAHA Robotics

- Beijing HTGD Technology Co., Ltd.

- Takara Leben Co., Ltd.

- Lorlin Test Systems

- Shenzhen Hangyu Communication Technology Co., Ltd.

- Elesys Co., Ltd.

Frequently Asked Questions

Analyze common user questions about the Test Handler market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is the primary function of a test handler in semiconductor manufacturing?

The primary function of a test handler is the automated physical management and movement of semiconductor devices (DUTs) between the production line and the Automatic Test Equipment (ATE). It ensures precise positioning, applies required thermal conditioning, and sorts tested devices based on electrical test results, crucial for high-volume quality control and throughput.

Which type of test handler is best suited for advanced packaging like SiP and BGA?

Pick-and-place handlers are best suited for advanced packaging (SiP, BGA, QFN) due to their high flexibility, superior positional accuracy, and ability to manage devices with non-standard geometries and high pin counts, contrasting with the high speed but lower flexibility of gravity handlers.

How does the proliferation of 5G and AI influence the demand for test handlers?

The proliferation of 5G and AI significantly boosts demand by requiring specialized handlers capable of high-frequency (RF) testing, higher parallelism, and extremely precise thermal control necessary to test complex, high-power chips (e.g., AI accelerators and 5G modems) accurately under simulated operating conditions.

What are the key technical challenges facing test handler manufacturers today?

Key technical challenges include achieving sub-micron accuracy for handling advanced fine-pitch packages, developing ultra-fast and wide-ranging thermal management systems, and ensuring handler compatibility with extremely high-speed electrical signals required for contemporary interfaces like PCIe 6.0 and DDR5 memory testing.

Which region dominates the global Test Handler Market and why?

Asia Pacific (APAC) dominates the global Test Handler Market because it hosts the vast majority of global semiconductor manufacturing, assembly, and test operations (OSATs and Foundries), particularly in Taiwan, South Korea, and Mainland China, driving massive volume-based capital expenditure.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager