Wafer Surface Planer Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 432629 | Date : Dec, 2025 | Pages : 246 | Region : Global | Publisher : MRU

Wafer Surface Planer Market Size

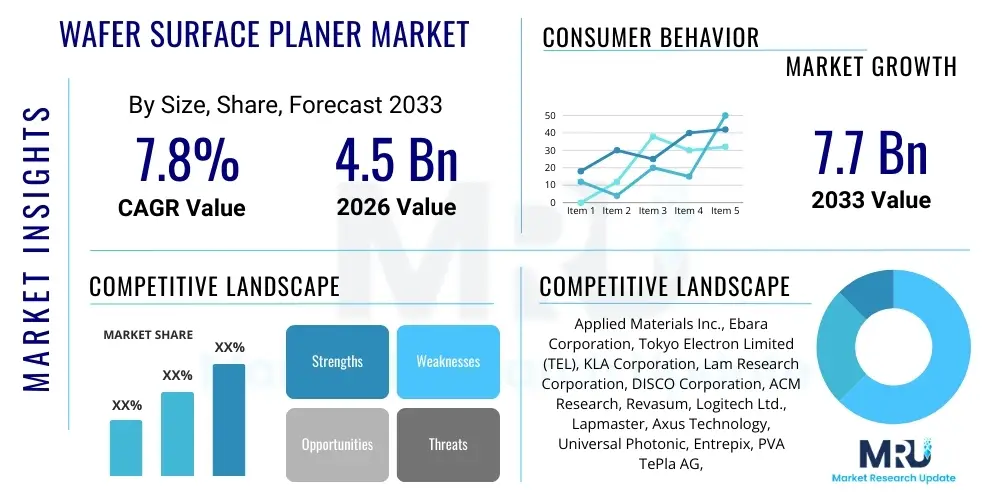

The Wafer Surface Planer Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 7.8% between 2026 and 2033. The market is estimated at USD 4.5 Billion in 2026 and is projected to reach USD 7.7 Billion by the end of the forecast period in 2033.

Wafer Surface Planer Market introduction

The Wafer Surface Planer Market encompasses sophisticated equipment and associated processes primarily used in Chemical Mechanical Planarization (CMP) operations during semiconductor manufacturing. CMP is a crucial step required to create ultra-flat surfaces on silicon wafers, enabling the subsequent deposition and patterning of intricate microelectronic circuits. As semiconductor technology advances towards sub-10nm nodes and 3D architectures like FinFET and 3D NAND, the demand for highly precise and defect-free wafer planarization becomes exponentially critical. These tools ensure global and local planarity, which is essential for achieving high lithography yield and reliable device performance.

Wafer surface planers, often integrated into complex CMP systems, utilize a combination of chemical reactions (driven by specialized slurries) and mechanical abrasion (using polishing pads) to remove excess material and smooth out topographical variations introduced during deposition processes. Major applications span across integrated circuit (IC) manufacturing, MEMS production, and advanced packaging technologies such as 2.5D and 3D integration. Key end-user sectors include pure-play foundries, Integrated Device Manufacturers (IDMs), and outsourced semiconductor assembly and test (OSAT) firms.

The market growth is fundamentally driven by the relentless pursuit of device miniaturization and the increasing complexity of semiconductor designs. The massive global investments in expanding fabrication capacity (fabs) in regions like Asia Pacific and North America, coupled with the escalating demand for high-performance computing (HPC), artificial intelligence (AI) accelerators, and advanced memory devices (DRAM and NAND), necessitate continuous upgrades and procurement of advanced wafer planarization systems capable of handling new materials and tighter tolerances. The transition to larger wafer sizes, such as 300mm and potential future migration to 450mm, also drives equipment replacement cycles.

Wafer Surface Planer Market Executive Summary

The Wafer Surface Planer Market is characterized by intense technological innovation, driven by the shift toward advanced process nodes and the proliferation of 3D device architectures, particularly in the memory sector (3D NAND). Business trends indicate strong capital expenditure cycles by major foundries and memory manufacturers, focusing heavily on acquiring next-generation CMP tools that offer higher throughput, superior uniformity, and reduced defectivity. Strategic partnerships between equipment manufacturers and slurry providers are increasing to develop co-optimized solutions. Furthermore, sustainability and operational efficiency are emerging trends, leading to the development of systems with lower chemical consumption and enhanced slurry recycling capabilities, addressing both cost pressures and environmental regulations.

Regionally, the Asia Pacific (APAC) continues its dominance, fueled by the massive concentration of semiconductor manufacturing capacity in Taiwan, South Korea, China, and Japan. China’s push for self-sufficiency in semiconductor manufacturing, backed by significant government subsidies, is generating substantial demand for high-end planarization equipment. North America and Europe remain pivotal centers for advanced R&D and prototype manufacturing, driving demand for the most sophisticated, precision-focused CMP tools, often tied to specialty semiconductor applications like compound semiconductors (GaAs, SiC) and photonics.

Segment trends reveal that the CMP equipment segment holds the largest market share, with rotary planarization systems dominating due to their established reliability and high throughput. However, the market is witnessing growing adoption of advanced in-situ metrology and post-CMP cleaning tools, crucial for maintaining ultra-clean surfaces prior to subsequent processing steps. The application segment is overwhelmingly driven by logic and memory IC manufacturing, with memory applications, particularly 3D NAND planarization, demanding increasingly specialized and complex multi-step CMP processes to handle high aspect ratios and novel materials like tungsten and cobalt.

AI Impact Analysis on Wafer Surface Planer Market

Common user questions regarding AI's impact on the Wafer Surface Planer Market frequently revolve around how artificial intelligence can address the fundamental challenges of process variability, yield loss, and the high cost associated with CMP. Users often inquire about the feasibility of using AI for real-time defect detection, optimizing polishing recipes for new materials, and predicting equipment failures before they occur. The key themes summarized from these inquiries highlight a strong industry expectation for AI to transform CMP from a largely empirical process into a highly predictive and automated one, thereby improving wafer uniformity, maximizing material utilization, and significantly reducing overall operational expenditure (OPEX) in the capital-intensive fabrication environment.

AI is fundamentally reshaping process control within CMP by utilizing machine learning algorithms to analyze vast datasets generated by metrology tools, polishing heads, and chemical delivery systems. This integration allows for dynamic adjustment of polishing pressure, slurry flow rate, and rotational speed in real-time, moving beyond traditional static recipe control. Such predictive capabilities are vital for minimizing non-uniformity across the wafer, which is a leading cause of yield degradation, especially as critical dimensions shrink to the nanometer scale.

Furthermore, AI-driven predictive maintenance (PdM) systems are being deployed to monitor the health of high-wear components like polishing pads, conditioning discs, and pumps. By analyzing acoustic, vibration, and performance data, AI models can forecast the optimal time for component replacement, significantly minimizing unscheduled downtime, which is extremely costly in 24/7 semiconductor fabrication plants. This shift from reactive or time-based maintenance to predictive maintenance is a major efficiency driver within the wafer surface planer market.

- AI enables real-time, adaptive control of CMP parameters (pressure, speed, flow) for improved uniformity.

- Predictive maintenance (PdM) leverages machine learning to forecast equipment component wear, maximizing uptime and reducing maintenance costs.

- Advanced image recognition AI enhances automated optical inspection (AOI) systems for faster and more accurate defect classification post-planarization.

- Machine learning algorithms optimize slurry consumption and chemical recycling processes, enhancing environmental sustainability and lowering OPEX.

- AI assists in rapid recipe development and tuning for new materials (e.g., Ruthenium, Molybdenum) introduced at advanced nodes, accelerating time-to-market.

DRO & Impact Forces Of Wafer Surface Planer Market

The Wafer Surface Planer Market is intensely influenced by competing forces of technological innovation, economic cycles, and stringent manufacturing requirements. Key drivers include the exponential increase in demand for advanced semiconductor devices, driven by 5G deployment, IoT expansion, and data center growth, necessitating higher volumes of wafers processed at sub-14nm nodes. Opportunities arise from the specialization required for emerging materials, such as SiC and GaN, and the massive investment wave in new fabrication facilities worldwide. However, the market faces significant restraints, notably the exceptionally high capital cost of advanced CMP equipment and the complex supply chain dependency on specialized component suppliers, which can be vulnerable to geopolitical tensions and trade restrictions. The interaction of these forces dictates market trajectory, pushing manufacturers toward highly automated and precise solutions.

One of the most powerful impact forces is the ongoing geopolitical competition and government intervention, particularly in the US, Europe, and China, aiming to secure domestic semiconductor supply chains. This has led to rapid capacity expansion and diversification of equipment procurement, stabilizing demand for specialized planarization tools. Simultaneously, the inherent technical challenge of CMP—achieving high material removal rates while maintaining zero defectivity and perfect planarity over large wafer areas—acts as a persistent barrier to entry, ensuring that market leadership remains consolidated among a few key equipment providers who possess the necessary proprietary technology and process know-how. The cost associated with R&D for developing slurries and pads compatible with complex multi-layer structures also contributes significantly to maintaining high barriers to entry.

The core drivers are the relentless scaling (More Moore) and integration (More than Moore) trends, which make the CMP step absolutely non-negotiable for stacking layers accurately. As device structures become three-dimensional, like in 3D NAND flash memory (where hundreds of layers are stacked), the cumulative non-planarity becomes magnified, making the surface planer's role critical for overall stack yield. The opportunity lies in providing turnkey solutions that integrate CMP, cleaning, and metrology into a single, highly controlled system. Conversely, a major restraint is the cyclical nature of the semiconductor industry, where periods of oversupply can temporarily halt equipment purchases, although the long-term trend remains positive due to structural demand growth in data-intensive applications.

Segmentation Analysis

The Wafer Surface Planer Market is comprehensively segmented based on the type of equipment, the materials processed, the primary application, and the technology utilized within the planarization system. This segmentation provides a granular view of market dynamics, highlighting areas of high growth and technological convergence. Key segments include the division between CMP equipment (the planer itself), conditioning equipment (for maintaining polishing pad effectiveness), and post-CMP cleaning systems, which are becoming increasingly integrated and crucial for minimizing surface defects. Application segmentation separates demand originating from memory fabrication (DRAM, NAND), logic manufacturing (CPUs, GPUs, ASICs), and specialized devices (MEMS, power semiconductors).

- By Equipment Type:

- Chemical Mechanical Planarization (CMP) Systems

- Post-CMP Cleaning Systems

- Pad Conditioners and Consumables

- By Application:

- Logic Devices (Advanced Nodes)

- Memory Devices (DRAM, 3D NAND)

- Power Devices and Optoelectronics

- MEMS and Sensors

- By Process Node:

- Below 10 nm

- 10 nm to 28 nm

- Above 28 nm

- By Technology:

- Rotary Planarization Systems

- Linear Planarization Systems

Value Chain Analysis For Wafer Surface Planer Market

The Wafer Surface Planer market operates within a highly sophisticated and interconnected value chain, beginning with the upstream supply of raw materials and extending to the end-users who fabricate the final electronic devices. Upstream analysis focuses on specialized material suppliers providing high-purity chemicals, polishing pads (e.g., polyurethane-based), and abrasive slurries (e.g., colloidal silica, ceria). These suppliers, often requiring intensive R&D to match new material requirements (e.g., tungsten, copper), hold significant influence over process effectiveness and cost. Equipment manufacturers then integrate these components, designing and assembling the complex planarization tools, characterized by high precision mechanical systems, advanced fluid delivery, and sophisticated software controls. This stage demands substantial intellectual property and capital investment, concentrating the market among a few global leaders.

The midstream involves the core manufacturing process where equipment is sold, installed, and maintained at semiconductor fabrication plants (fabs). The distribution channel is predominantly direct, given the high cost, customization, and need for specialized support (installation, training, maintenance contracts). Direct sales ensure maximum control over highly technical deployment and intellectual property protection. Indirect channels are rarely used for the primary CMP tools but may be employed for distributing certain consumables or lower-tier ancillary equipment through regional agents or distributors.

Downstream analysis focuses on the final consumers: Integrated Device Manufacturers (IDMs) like Intel and Samsung, and pure-play foundries such as TSMC and GlobalFoundries. These entities utilize the wafer surface planers to execute critical steps in their front-end manufacturing processes. The demand for planers is therefore directly linked to the capital expenditure cycles of these major semiconductor players. The success of the planarization step directly impacts the yield and performance of the final chip, making the performance and reliability of the equipment paramount to the entire downstream electronics industry. The feedback loop between end-users and equipment manufacturers is vital for continuous process improvement and innovation.

Wafer Surface Planer Market Potential Customers

The primary customers for Wafer Surface Planer equipment and associated consumables are organizations involved in the high-volume manufacturing and advanced research of semiconductor wafers. These include large-scale Integrated Device Manufacturers (IDMs) that design, fabricate, and sell their own chips, such as memory giants and microprocessor manufacturers. For these IDMs, planarization capability directly influences their ability to transition to next-generation nodes and maintain a competitive edge in memory and logic performance. CMP tools are indispensable for their front-end-of-line (FEOL) and back-end-of-line (BEOL) processes.

A second crucial customer segment comprises pure-play foundries, which specialize solely in wafer fabrication for fabless design companies. As the leading-edge foundry model demands handling the most complex and tightest tolerances (e.g., 5nm and below), foundries are consistently the earliest and largest adopters of the newest planarization technologies. Their business model relies heavily on high yield rates and rapid process migration, making the choice of wafer surface planer technology a critical operational decision.

Beyond the core IC manufacturing sector, key potential buyers also include manufacturers of specialized devices, such as power electronics utilizing Silicon Carbide (SiC) or Gallium Nitride (GaN) wafers, and producers of Micro-Electro-Mechanical Systems (MEMS) and sensors. Although these applications may involve smaller wafer volumes or different material sets, the requirement for ultra-flat surfaces remains essential for bonding, lithography, and integration. Additionally, academic and independent semiconductor research consortia often procure specialized or prototype planarization equipment for materials science research and process development.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | USD 4.5 Billion |

| Market Forecast in 2033 | USD 7.7 Billion |

| Growth Rate | 7.8% CAGR |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | Applied Materials Inc., Ebara Corporation, Tokyo Electron Limited (TEL), KLA Corporation, Lam Research Corporation, DISCO Corporation, ACM Research, Revasum, Logitech Ltd., Lapmaster, Axus Technology, Universal Photonic, Entrepix, PVA TePla AG, ZEISS Group, SEMES, STRASBAUGH, SPEEDFAM. |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Wafer Surface Planer Market Key Technology Landscape

The technology landscape of the Wafer Surface Planer Market is dominated by continuous advancements in Chemical Mechanical Planarization (CMP) equipment, driven primarily by the need to handle new materials and geometries at advanced semiconductor nodes (e.g., 7nm, 5nm, and 3nm). A key technological focus is on enhancing process control through sophisticated in-situ monitoring tools. These advanced systems integrate sensors, optics, and software to measure film thickness and uniformity during the polishing process, allowing for dynamic adjustments and precise endpoint detection. This move towards real-time feedback loops is crucial for minimizing over-polishing or under-polishing, which can severely impact device performance and yield, particularly in high-aspect-ratio 3D structures.

Another major area of innovation lies in the development of specialized slurries and polishing pads. As manufacturers transition from copper and tungsten to exotic materials like cobalt, ruthenium, and various high-k/metal gate stacks, the chemical and mechanical properties of the consumables must be meticulously tailored. Slurry development now emphasizes selectivity—the ability to remove one material precisely while minimally affecting adjacent materials—critical for maintaining complex interconnect structures. Furthermore, pad technology is evolving to improve stability, lifetime, and conditioning effectiveness, often incorporating advanced material compositions and novel micro-texture designs to ensure consistent wafer contact and material removal rates across the entire wafer surface.

Finally, post-CMP cleaning technology represents an indispensable part of the overall planarization process. The introduction of abrasive particles and chemical residues during CMP necessitates highly efficient and gentle cleaning techniques to prevent micro-scratching and metallic contamination. Current technological advancements focus on megasonic cleaning, advanced brush scrubbing, and precise control over dilute chemical chemistries. The integration of high-purity water systems and advanced drying technologies (e.g., Marangoni drying) ensures that the wafer surface is atomically clean and ready for subsequent high-temperature processing steps. The trend is towards fully automated, modular cleaning tools that offer customizable chemistries and sequences to address the diverse contamination profiles resulting from different CMP processes.

Regional Highlights

The global Wafer Surface Planer Market exhibits distinct regional dynamics heavily correlated with semiconductor manufacturing capacity and technological leadership. Asia Pacific (APAC) holds the undeniable majority share, serving as the global epicenter for high-volume semiconductor production. Within APAC, countries like Taiwan (driven by leading foundries), South Korea (dominated by memory giants), and China (fueled by aggressive self-sufficiency drives and massive government investment in new fabs) are the primary consumers of wafer surface planarization equipment. China's recent capacity expansion initiatives, aimed at scaling up domestic IC production, generate enormous, continuous demand for both mature and advanced CMP systems. South Korea remains critical due to its dominant position in 3D NAND and high-density DRAM production, which necessitates the most advanced multi-step planarization tools.

North America, while possessing a smaller share in high-volume fabrication compared to APAC, remains a critical hub for high-end equipment R&D, specialized semiconductor manufacturing (e.g., aerospace, defense), and the production of cutting-edge microprocessors. The presence of leading equipment suppliers and major IDMs drives demand for highly customized, research-grade, and pilot-line planarization tools. Recent government initiatives aimed at onshore manufacturing, such as the CHIPS Act, are stimulating significant capital investment, leading to the construction of new mega-fabs that will require vast quantities of new CMP equipment in the coming decade, increasing North America's market relevance.

Europe’s market is characterized by specialized manufacturing, particularly in the automotive, industrial, and power electronics sectors (SiC and GaN). Countries such as Germany and France are investing in localized semiconductor supply chains (e.g., the European Chips Act), fostering a moderate but highly focused demand for planarization tools tailored for compound semiconductor processing, which often requires robust equipment capable of handling harder, more brittle materials than traditional silicon. The region also hosts key research institutions driving innovation in advanced materials and packaging technologies, ensuring a continuous, albeit moderate, demand for high-precision planarization and finishing systems.

- Asia Pacific (APAC): Dominates the market due to the concentration of global foundries and memory manufacturers (Taiwan, South Korea, China). Massive ongoing capacity expansion in China drives high equipment procurement rates.

- North America: Crucial for advanced R&D, specialized manufacturing, and the headquarters of major equipment providers. Demand is surging due to government-backed reshoring initiatives and new fab construction.

- Europe: Focuses on specialized applications, particularly automotive power semiconductors (SiC/GaN) and industrial electronics. Investments are targeted towards securing regional supply chains and advanced packaging research.

- Rest of the World (ROW): Includes emerging markets in Latin America and the Middle East, characterized by early-stage investment in localized assembly or specialized niche manufacturing, contributing a smaller, but growing, segment of demand.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Wafer Surface Planer Market.- Applied Materials Inc.

- Ebara Corporation

- Tokyo Electron Limited (TEL)

- KLA Corporation

- Lam Research Corporation

- DISCO Corporation

- ACM Research

- Revasum

- Logitech Ltd.

- Lapmaster

- Axus Technology

- Universal Photonic

- Entrepix

- PVA TePla AG

- ZEISS Group

- SEMES

- STRASBAUGH

- SPEEDFAM

- Advanced Grinding Technology (AGT)

- Fujimi Incorporated (Slurry Focus)

Frequently Asked Questions

What is the primary function of a Wafer Surface Planer in semiconductor fabrication?

The primary function of a Wafer Surface Planer, typically integrated into a Chemical Mechanical Planarization (CMP) system, is to smooth and flatten the surface of a silicon wafer. This process is critical for removing non-uniform topography introduced during deposition steps, ensuring the wafer surface achieves global and local planarity required for high-resolution photolithography and successful stacking of layers in advanced integrated circuits.

Which technological trends are currently driving the demand for advanced CMP tools?

Demand is driven by the industry's continuous scaling below 10nm process nodes and the proliferation of three-dimensional device architectures, such as 3D NAND flash memory and FinFET transistors. These complex structures necessitate ultra-precise planarization, highly selective slurries, and advanced in-situ metrology to manage high aspect ratios and novel materials (e.g., cobalt, ruthenium) crucial for modern interconnects.

How is Artificial Intelligence (AI) being utilized to enhance Wafer Surface Planing?

AI is employed to enhance process control and equipment reliability. Machine learning algorithms analyze real-time data from polishing tools to dynamically optimize parameters (pressure, speed) for improved uniformity and yield. Additionally, AI-driven predictive maintenance (PdM) helps forecast equipment component failure, drastically reducing unscheduled downtime in fabrication facilities.

Which geographical region represents the largest market share for Wafer Surface Planer equipment?

The Asia Pacific (APAC) region currently holds the largest market share, driven by major semiconductor manufacturing nations including Taiwan, South Korea, and Mainland China. This region concentrates the highest volume of global foundry and memory manufacturing capacity, leading to the greatest capital expenditure on planarization and associated cleaning equipment.

What are the key consumables associated with Wafer Surface Planer operations?

The key consumables in wafer surface planarization include abrasive slurries (mixtures of specialized chemicals and nanoparticles, such as colloidal silica or ceria), polishing pads (polyurethane-based discs that provide the mechanical action), and conditioning discs used to maintain the optimal surface texture of the polishing pads during operation. These consumables represent a significant portion of the ongoing operational expenditure (OPEX).

Detailed Market Dynamics and Competitive Landscape

The competitive landscape of the Wafer Surface Planer Market is highly concentrated, dominated by a few major players who command significant market share due to substantial patent portfolios, deep process know-how, and long-standing relationships with tier-one semiconductor manufacturers. The market is characterized by fierce competition centered on two primary factors: throughput efficiency and process capability at the most advanced nodes. Equipment manufacturers must continuously invest heavily in research and development to address the evolving complexity of planarization, particularly the chemical and mechanical challenges posed by multi-layer stacks and integration of new materials like high-K dielectrics and novel metals. Successful market penetration depends not only on selling the hardware but also on providing comprehensive service, support, and co-optimization with proprietary slurries and pad systems.

The development cycle for new CMP equipment often spans several years and requires extensive collaboration with leading IDMs and foundries to ensure the tool meets highly specific manufacturing requirements. This necessitates robust partnerships and joint development programs, further solidifying the position of incumbent market leaders. Smaller or emerging competitors often focus on specialized niche markets, such as legacy nodes, specialized materials (e.g., sapphire, SiC), or providing advanced post-CMP cleaning or metrology solutions, rather than competing directly in the mainstream high-volume logic and memory CMP equipment space. Mergers, acquisitions, and strategic alliances are common tactics employed to rapidly acquire necessary intellectual property or expand geographic reach, especially into fast-growing markets like China.

Furthermore, the high barrier to entry is maintained by the necessity for equipment manufacturers to guarantee ultra-low defectivity rates (often measured in defects per million wafers) and exceptional wafer-to-wafer uniformity. Any minor deviation in planarity can result in catastrophic yield loss for a multi-billion-dollar fab. Consequently, customers prioritize proven reliability and established process heritage over cost savings when procuring primary planarization tools. This preference ensures that market leaders who can demonstrate decades of flawless performance and superior technical support maintain their dominant positions, forcing smaller entrants to overcome substantial credibility hurdles before gaining adoption at the leading edge of semiconductor manufacturing.

Impact of New Materials and Emerging Applications

The constant introduction of new materials in semiconductor fabrication presents both the biggest challenge and the greatest opportunity for the Wafer Surface Planer Market. Traditional planarization techniques optimized for Silicon Dioxide (SiO2) and Tungsten (W) are often inadequate for handling novel materials designed to enhance device speed and power efficiency, such as Cobalt and Ruthenium for low-resistance interconnects, or specialized amorphous carbons and polymers. These new materials require fundamentally new CMP slurries and processes that achieve high removal selectivity and low friction while minimizing surface damage. Equipment manufacturers must design systems capable of managing a wider range of chemical compositions and mechanical parameters dynamically.

The complexity is further amplified in emerging applications like Silicon Carbide (SiC) and Gallium Nitride (GaN) for power electronics. These compound semiconductors are significantly harder and more brittle than silicon, requiring specialized planarization techniques that focus on sub-surface damage removal (SSD) and achieving an atomic-level finish with minimal surface roughness (Ra). The market for SiC/GaN planarization tools is growing rapidly, driven by the electric vehicle (EV) market and high-efficiency power management systems. This niche segment often utilizes adapted versions of conventional CMP, but with highly specialized polishing pads and extremely aggressive chemical mechanical actions.

Another significant driver is advanced packaging (2.5D/3D integration), where through-silicon via (TSV) technology necessitates precise thinning and planarization of wafers to depths often measured in just tens of micrometers. TSV CMP requires extremely high uniformity across the wafer to ensure successful bonding of multiple chips. The equipment in this sector must be capable of handling extremely thin, delicate wafers without breakage, leading to innovations in handling systems, stress management during polishing, and highly controlled wafer clamping mechanisms. These demanding applications ensure a high-value segment within the overall wafer surface planer market, fostering innovation distinct from traditional front-end-of-line IC manufacturing.

Future Trends and Growth Opportunities

The future trajectory of the Wafer Surface Planer Market is highly dependent on achieving unprecedented levels of precision and automation. One significant trend is the move toward fully closed-loop process control, leveraging advanced analytics and sensor fusion to make instantaneous adjustments to the CMP process. This transition minimizes reliance on manual intervention and traditional metrology pauses, significantly boosting throughput and consistency. The integration of advanced computational fluid dynamics (CFD) modeling into the tool design phase is also becoming standard, allowing engineers to predict and optimize slurry flow patterns and material removal uniformity before physical prototyping, thus accelerating tool development cycles.

Growth opportunities are strongly linked to the expansion of mature nodes (28nm and above) in response to global geopolitical efforts to diversify supply chains, especially for automotive and IoT chip production. While the leading-edge nodes receive high visibility, the sustained demand for established technology nodes, often manufactured in new fabs across emerging regions, guarantees a robust market for proven, high-throughput legacy CMP systems. Furthermore, the push towards greater sustainability in manufacturing opens opportunities for planarization system manufacturers who can deliver equipment optimized for reduced water usage, lower chemical consumption, and effective recycling of costly slurries, appealing to foundries facing increasing regulatory and corporate social responsibility (CSR) pressure.

In terms of technological innovation, the market is exploring alternatives or complements to traditional rotary CMP, such as linear polishing systems, which offer potential advantages in uniformity for extremely large wafers or specialized material removal patterns. The convergence of CMP, grinding, and polishing technologies into unified systems capable of handling both bulk material removal and precision surface finishing is another emerging trend, particularly relevant for compound semiconductor manufacturing and advanced packaging where initial wafer preparation is as critical as the final planarization step. These factors collectively indicate a market that, while mature in its core technology, is undergoing rapid transformation driven by material science and data-intensive process control.

Regulatory and Environmental Impact

The operation of Wafer Surface Planer equipment, particularly the CMP process, carries significant environmental implications due to the extensive use of chemicals, abrasive nanoparticles in slurries, and high volumes of deionized water for post-CMP cleaning. Regulatory pressures, especially in regions with stringent environmental standards like Europe and parts of Asia, are increasingly influencing equipment design. Manufacturers are responding by focusing on 'Green CMP' technologies, which aim to reduce the consumption and discharge of hazardous materials. This includes the development of environmentally benign slurries that are easier to neutralize and recycle, as well as optimizing chemical delivery systems to minimize waste.

Handling and disposal of used CMP consumables, specifically polishing pads and spent slurries, pose a logistical and environmental challenge. Slurries, containing metallic residues and abrasive particles, require specialized treatment before discharge. This drives demand for integrated filtration and recycling systems that can recover and reuse the costly chemical components, mitigating both environmental impact and operational costs. For equipment manufacturers, meeting increasingly tight effluent standards has become a non-negotiable design requirement, promoting the development of closed-loop water and chemical management solutions integrated directly into the planarization tool.

Furthermore, worker safety and exposure limits related to chemical handling and nanoparticle inhalation require strict adherence to regulatory standards (e.g., OSHA, REACH). Wafer Surface Planer systems must incorporate advanced automation features, including robotic chemical handling and fully enclosed processing chambers, to minimize human contact with potentially hazardous materials. Compliance with international standards for energy efficiency (SEMI standards) is also becoming important, pushing manufacturers to design tools that consume less power during idle and operational states, aligning with the broader industry commitment to reducing the overall carbon footprint of semiconductor manufacturing.

Intellectual Property and Patent Landscape

The Wafer Surface Planer Market is underpinned by a dense and complex web of intellectual property (IP), reflecting decades of intensive R&D efforts by key players. Patents cover virtually every aspect of the CMP process, ranging from novel mechanical designs (e.g., polishing head kinematics, platen rotational control), specific slurry compositions and conditioning methods, to sophisticated in-situ metrology techniques and advanced endpoint detection algorithms. The control over critical IP is a primary factor determining market share and technological leadership, making the patent landscape highly litigious.

Major equipment providers leverage their extensive patent portfolios to secure and maintain exclusivity over high-performance solutions, often requiring cross-licensing agreements or strategic partnerships to navigate the complex legal environment. The most valuable IP relates to minimizing defectivity at the nanoscale and achieving high removal selectivity necessary for multi-material structures (e.g., copper/barrier layer CMP). Any new entrant must carefully navigate this established IP space, which acts as a formidable barrier to market entry for generalists or companies lacking specialized expertise.

A recent trend in the IP landscape focuses on software and data analytics patents. As AI and machine learning become integrated into process control, IP is increasingly being generated around proprietary algorithms for predictive maintenance, real-time recipe tuning, and virtual metrology (estimating wafer state without physical sensors). This shift indicates that future competitive advantages will rely not just on superior hardware design but also on the intelligent management and exploitation of vast amounts of process data, further consolidating technological leadership among those companies that can seamlessly combine chemical, mechanical, and computational expertise.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager