Advanced Packaging Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033 (Financial Impact Analysis)

ID : MRU_ 433426 | Date : Dec, 2025 | Pages : 243 | Region : Global | Publisher : MRU

Advanced Packaging Market Size

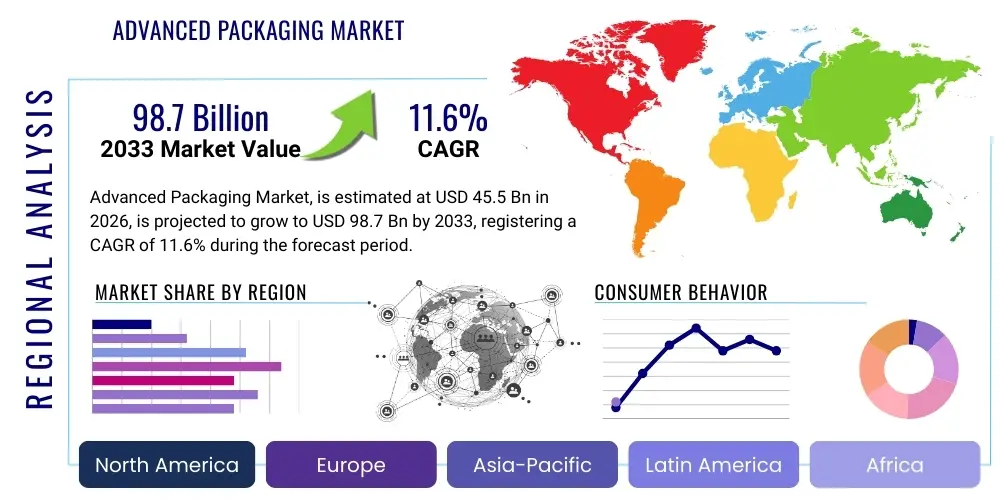

The Advanced Packaging Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 11.6% between 2026 and 2033. The market is estimated at USD 45.5 Billion in 2026 and is projected to reach USD 98.7 Billion by the end of the forecast period in 2033. This robust expansion is primarily fueled by the accelerating demand for high-performance computing (HPC), artificial intelligence (AI) accelerators, and the pervasive rollout of 5G infrastructure, necessitating greater integration density and improved power efficiency in semiconductor devices.

Advanced Packaging Market introduction

The Advanced Packaging Market encompasses sophisticated techniques used to interconnect and protect semiconductor dies, moving beyond traditional wire bonding and single-chip molding. These methods—including 2.5D and 3D integration, Fan-Out Wafer Level Packaging (FO-WLP), and Through-Silicon Vias (TSVs)—are critical enablers for heterogeneous integration, allowing multiple components (such as logic, memory, and specialized accelerators) to be packaged together in a single, compact module. This paradigm shift in packaging is essential for addressing the physics limitations of Moore's Law, facilitating continued performance scaling, and enhancing device functionality while reducing form factor and power consumption.

Major applications driving this market include high-end processors used in data centers and cloud infrastructure, sophisticated sensor arrays in autonomous vehicles, complex system-on-chips (SoCs) for premium consumer electronics, and high-bandwidth memory (HBM) modules integral to AI training and inference platforms. The primary benefit derived from advanced packaging is the significant improvement in interconnect speed and density, which translates directly into higher system bandwidth, lower latency, and superior thermal management. Furthermore, the modularity inherent in techniques like chiplet integration allows semiconductor manufacturers to mix and match dies fabricated using different process nodes, optimizing cost and time-to-market.

Key driving factors include the explosion of data requiring immediate processing at the edge and in the cloud, the increasing complexity of semiconductor designs that cannot be economically manufactured monolithically, and consumer demand for smaller, more powerful, and energy-efficient devices. The adoption of 5G and subsequent 6G wireless standards also mandates high-frequency performance and stringent signal integrity, achievable primarily through advanced packaging solutions. Geopolitical emphasis on domestic semiconductor manufacturing capacity further supports investment in outsourced semiconductor assembly and test (OSAT) services globally, fostering innovation in packaging technologies.

Advanced Packaging Market Executive Summary

The Advanced Packaging Market is characterized by intense technological competition and significant capital investment, reflecting the transition from monolithic scaling to heterogeneous integration. Business trends show a strategic divergence between Integrated Device Manufacturers (IDMs) enhancing internal packaging capabilities and major Outsourced Semiconductor Assembly and Test (OSAT) vendors specializing in high-volume, advanced processes like FO-WLP and 3D stacking. A dominant trend is the rise of chiplet architecture, where standardized die interfaces allow designers to build complex systems modularly, reducing yield loss risks and accelerating design cycles, particularly for specialized processors targeting AI and machine learning applications.

Regionally, the Asia Pacific (APAC) continues its unparalleled dominance, largely due to the concentration of major foundry operations, high-volume manufacturing facilities, and the headquarters of leading OSAT providers in countries such as Taiwan, South Korea, and China. This region acts as the global epicenter for both demand and supply of advanced packaging services, benefiting from robust government incentives and an established supply chain ecosystem. While North America and Europe primarily drive innovation and captive demand (especially for high-performance computing and defense applications), APAC remains crucial for the actual volume production and commercialization of new packaging types.

Segment trends highlight the exceptional growth of 3D ICs and 2.5D interposers, driven explicitly by the requirements of High Bandwidth Memory (HBM) integration alongside logic processors, which is foundational for modern AI accelerators. Within the technology types, Fan-Out Wafer Level Packaging (FO-WLP) is experiencing high adoption due to its balance of thinness, performance, and cost-effectiveness compared to traditional flip-chip BGA, particularly within mobile and networking applications. The application segment growth is overwhelmingly focused on data centers and high-performance computing (HPC), followed closely by the rapidly expanding automotive sector, where advanced packaging ensures reliability and performance for ADAS (Advanced Driver-Assistance Systems) and infotainment.

AI Impact Analysis on Advanced Packaging Market

User inquiries regarding the influence of Artificial Intelligence on the Advanced Packaging Market overwhelmingly center on two key themes: how advanced packaging enables the requisite computational density for large language models (LLMs) and generative AI, and the thermal management challenges associated with powerful AI accelerators. Users are keen to understand the specific role of 2.5D and 3D stacking in overcoming the memory wall bottleneck—the fundamental limitation where data transfer speeds between memory and processing units hinder overall AI performance. The consensus expectation is that AI demand will not only increase the volume of advanced packaged chips but fundamentally alter the technical requirements, pushing the envelope for power delivery networks and inter-die communication bandwidth.

The demand created by AI systems necessitates the integration of vast arrays of processing cores and high-speed memory within a small footprint, a feat nearly impossible with traditional packaging. Advanced packaging, particularly utilizing silicon interposers (2.5D) and direct chip stacking (3D), allows for extremely short interconnects between the compute elements and HBM stacks. This ultra-short path drastically reduces energy consumption per bit transferred and maximizes data throughput, making complex AI training efficient and feasible. Consequently, AI applications are the primary catalyst accelerating the commercial maturity and adoption rates of the most complex and high-cost packaging solutions.

Furthermore, AI hardware, characterized by high power consumption (often exceeding 700W per package in high-end accelerators), generates significant thermal load. Advanced packaging designs are integral to effective thermal dissipation. Techniques like incorporation of microfluidic channels or specialized thermal interface materials directly into the package structure are being explored. The need for precise power delivery and reliable thermal performance in these high-power density environments places stringent demands on substrate materials, bonding techniques, and overall package reliability, driving innovation specifically geared towards AI accelerator reliability and longevity.

- AI demand drives exponential growth in 2.5D/3D integration adoption for high-bandwidth memory (HBM) stacking.

- Advanced packaging is mandatory for minimizing the memory wall bottleneck in large AI models and deep learning applications.

- Increased power density in AI accelerators mandates the development of sophisticated thermal management solutions integrated directly into the package structure.

- Chiplet architecture, enabled by advanced packaging standards like UCIe, becomes the default methodology for building scalable AI processors.

- AI tools are increasingly used in the design and optimization phase of advanced packaging layouts to maximize signal integrity and power efficiency.

DRO & Impact Forces Of Advanced Packaging Market

The market dynamics for advanced packaging are characterized by a strong interplay between technological pull from emerging applications and inherent economic and manufacturing challenges. The primary driver is the undeniable necessity for heterogeneous integration to maintain performance gains in the face of diminishing returns from traditional transistor scaling, supported by massive investment from technology giants requiring specialized chips for AI and cloud infrastructure. However, the market faces significant restraints, most notably the extremely high capital expenditure required for setting up advanced packaging lines and the complexity involved in managing the multi-vendor supply chain for chiplets. Opportunities abound in niche markets like medical devices and IoT, demanding specialized miniaturized solutions, and in the establishment of standardized interfaces and co-design methodologies to simplify the integration process. These factors collectively exert a powerful impact force, tilting the industry towards collaborative models and continuous, high-speed innovation in materials science and interconnect technology.

Specific drivers include the global rollout of 5G and future 6G networks, which require highly integrated radio frequency (RF) modules with low loss and high linearity, achievable through advanced packaging techniques like System-in-Package (SiP). Furthermore, the push towards autonomous driving elevates the need for extremely reliable, temperature-tolerant, and powerful computing units within vehicles, relying on robust 2.5D and 3D packaged devices. These drivers ensure sustained investment in new capacity, especially in Asia, where OSATs are rapidly expanding their capabilities to meet high-volume demand from leading fabless companies.

Conversely, the high barrier to entry due to R&D intensity and the requirement for highly precise manufacturing equipment (such as hybrid bonding tools) acts as a significant restraint, limiting the number of capable suppliers globally. Another major impact force is the geopolitical environment, specifically trade tensions, which have accelerated the regionalization of supply chains. This shift, while initially disruptive, presents an opportunity for North America and Europe to invest heavily in onshore advanced packaging facilities, mitigating long-term supply chain risks and fostering innovation in diverse geographical hubs. Successfully navigating the high manufacturing costs and intellectual property concerns surrounding proprietary packaging technologies remains critical for sustained growth.

Segmentation Analysis

The Advanced Packaging Market is extensively segmented based on technology type, application, and end-user, reflecting the diverse requirements across the semiconductor ecosystem. The segmentation by technology type, which includes Flip Chip (FC), Fan-Out Wafer Level Packaging (FO-WLP), Fan-In Wafer Level Packaging (FI-WLP), and 2.5D/3D Integrated Circuits (ICs), dictates the performance, size, and cost characteristics of the resulting semiconductor device. The most significant growth is projected in the 2.5D/3D IC segment due to its necessity in high-performance computing (HPC). Furthermore, segmentation by application, spanning communication, automotive, industrial, and consumer electronics, showcases the varying performance demands, with HPC and servers driving the highest revenue share. Analyzing these segments provides strategic clarity regarding investment priorities and technological roadmap development.

- By Technology Type:

- Flip Chip (FC)

- Fan-Out Wafer-Level Packaging (FO-WLP)

- Fan-In Wafer-Level Packaging (FI-WLP)

- 2.5D/3D ICs (Interposers, Through-Silicon Vias)

- System-in-Package (SiP)

- Wafer-Level Chip Scale Packaging (WLCSP)

- By Application:

- High-Performance Computing (HPC) & Data Centers

- Communication (5G infrastructure, Networking)

- Automotive (ADAS, Infotainment)

- Consumer Electronics (Smartphones, Wearables)

- Industrial & Medical

- By End-User:

- Integrated Device Manufacturers (IDMs)

- Outsourced Semiconductor Assembly and Test (OSAT) Companies

- Foundries

- Fabless Semiconductor Companies

Value Chain Analysis For Advanced Packaging Market

The Advanced Packaging value chain is complex and highly specialized, beginning upstream with critical raw material suppliers and equipment manufacturers. Upstream activities involve the production of specialized materials such as high-performance organic substrates, advanced polymer dielectrics, specialized solder materials (micro-bumps), and most critically, sophisticated equipment used for lithography, sputtering, chemical mechanical planarization (CMP), and hybrid bonding. These suppliers are foundational, as innovations in packaging performance often hinge on the limits of material science and manufacturing precision. Companies dominating this segment are often based in Japan, the US, and Europe, providing high-precision tools necessary for sub-micron interconnects.

The midstream segment is dominated by Integrated Device Manufacturers (IDMs), Foundries (such as TSMC and Samsung), and OSAT service providers (e.g., ASE and Amkor). Foundries play an increasingly critical role by offering integrated frontend-to-backend services, especially for 2.5D and 3D stacking solutions, often incorporating their proprietary interposer and TSV technologies. OSATs focus on high-volume, cost-effective advanced solutions like Fan-Out and SiP. The distribution channels for these services are primarily direct, involving long-term strategic contracts between the semiconductor manufacturers (fabless and IDMs) and the packaging service providers. Indirect channels are less common but may include technology licensing agreements or specialized design house partnerships.

Downstream activities involve the integration of the packaged devices into end-user products across various sectors. The final customers—Tier 1 automotive suppliers, smartphone manufacturers, cloud service providers (hyperscalers), and military/aerospace contractors—provide essential feedback loops regarding package reliability, thermal performance, and overall cost targets. The tightness of integration required for advanced packaging means there is heavy co-design and collaboration between the downstream users and the midstream packaging providers, ensuring the package meets system-level performance requirements, particularly for high-density, mission-critical applications.

Advanced Packaging Market Potential Customers

The primary customers for advanced packaging technologies are entities demanding ultra-high performance, significant miniaturization, and enhanced reliability in their semiconductor components. Hyperscale cloud providers like AWS, Google, and Microsoft are major buyers, as they require custom AI accelerators and high-performance CPUs/GPUs packaged using 2.5D and 3D integration to power their massive data centers and AI operations. Their purchasing decisions are driven purely by performance metrics, power efficiency, and the ability to rapidly deploy customized silicon solutions, often relying on chiplet architecture enabled by advanced packaging.

Another crucial customer segment is the consumer electronics industry, dominated by major smartphone and wearable device manufacturers (e.g., Apple, Samsung, Huawei). For these companies, the drivers are form factor reduction and increased battery life, leading to high adoption of Fan-Out Wafer Level Packaging (FO-WLP) and System-in-Package (SiP) technologies. These advanced solutions allow for complex functions (like modem, processor, and power management units) to be stacked or integrated side-by-side within extremely thin packages, differentiating high-end consumer products based on integration density and aesthetic design.

Furthermore, the automotive sector represents a rapidly growing and demanding customer base. Autonomous driving systems and advanced driver-assistance systems (ADAS) require powerful, reliable processors that can withstand harsh operating environments (extreme temperature variations, vibration). Tier 1 automotive suppliers and Original Equipment Manufacturers (OEMs) demand robust packaging solutions, such as embedded die technology and highly reliable flip-chip modules, ensuring decades-long operational life under stress. Reliability and zero-defect quality standards are paramount in this segment, translating into premium pricing for advanced packaging solutions that meet these rigorous safety specifications.

| Report Attributes | Report Details |

|---|---|

| Market Size in 2026 | USD 45.5 Billion |

| Market Forecast in 2033 | USD 98.7 Billion |

| Growth Rate | 11.6% CAGR |

| Historical Year | 2019 to 2024 |

| Base Year | 2025 |

| Forecast Year | 2026 - 2033 |

| DRO & Impact Forces |

|

| Segments Covered |

|

| Key Companies Covered | Taiwan Semiconductor Manufacturing Company Limited (TSMC), ASE Technology Holding Co., Ltd. (ASEH), Amkor Technology, Inc., Samsung Electronics Co., Ltd., Intel Corporation, JCET Group Co., Ltd., Powertech Technology Inc. (PTI), United Microelectronics Corporation (UMC), KYEC, UTAC Holdings Ltd., Shinko Electric Industries Co., Ltd., Toshiba Corporation, Broadcom Inc., IBM, Deca Technologies, S-Semi, Tianshui Huatian Technology Co., Ltd., Hana Micron Inc., Chipbond Technology Corporation. |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Enquiry Before Buy | Have specific requirements? Send us your enquiry before purchase to get customized research options. Request For Enquiry Before Buy |

Advanced Packaging Market Key Technology Landscape

The technological landscape of advanced packaging is rapidly evolving, moving away from simple protective casing toward sophisticated functional integration modules. A foundational technology driving this revolution is 2.5D integration, which utilizes a silicon or organic interposer to bridge multiple chips (e.g., logic and HBM) horizontally, providing extremely high-density and high-speed connections that bypass traditional printed circuit board (PCB) limitations. While 2.5D addresses immediate bandwidth needs for HPC and AI, it faces challenges related to the cost and size of the interposer, pushing innovation towards cost-optimized solutions like interposers based on glass or organic materials.

The next frontier is 3D integration, specifically 3D stacking of active dies, achieved through Through-Silicon Vias (TSVs) and advanced micro-bump bonding, and increasingly, hybrid bonding. Hybrid bonding, which directly connects copper pads without requiring micro-bumps, offers vastly higher interconnect density and faster data transmission, positioning it as the key enabling technology for future high-density memory and logic stacks. Currently, 3D integration is vital for high-bandwidth memory (HBM) and increasingly relevant for stacking homogeneous and heterogeneous logic dies to achieve maximum volumetric efficiency.

Concurrently, Wafer Level Packaging (WLP), encompassing both Fan-In (FI-WLP) and Fan-Out (FO-WLP), continues to gain market share, particularly in mobile and automotive applications where size and profile are critical. FO-WLP is especially disruptive as it eliminates the traditional organic substrate, achieving near-IC performance in a package, offering better thermal performance, and allowing for greater I/O expansion compared to the die size. Furthermore, the industry is heavily invested in establishing the Universal Chiplet Interconnect Express (UCIe) standard, which is not a packaging technology itself but dictates the electrical and physical interfaces necessary for reliable integration of chiplets from different vendors, thereby maximizing the economic benefits derived from advanced packaging infrastructures.

Regional Highlights

- Asia Pacific (APAC): APAC is the unquestioned global leader in the Advanced Packaging Market, driven by the presence of all major foundries (TSMC, Samsung), leading OSAT players (ASE, Amkor, JCET), and a substantial portion of the world's high-volume semiconductor manufacturing base. The region benefits from substantial government support, robust infrastructure, and a mature supply chain ecosystem. Taiwan and South Korea lead the technological front in 2.5D/3D integration and high-end Fan-Out solutions, catering to global demand for AI and mobile processors.

- North America: North America is the primary center for demand generation, particularly for cutting-edge AI, cloud computing, and high-performance server chip design (Intel, AMD, Nvidia). While a significant portion of manufacturing is outsourced, there is increasing strategic investment (driven by geopolitical initiatives like the CHIPS Act) to build domestic advanced packaging capacity, focusing on highly specialized, high-security, and high-margin packaging solutions necessary for aerospace and defense applications.

- Europe: The European market demonstrates steady growth, primarily driven by the automotive, industrial automation, and medical device sectors. Europe specializes in highly reliable, low-power integrated solutions, favoring System-in-Package (SiP) and embedded die technologies that ensure robustness for harsh environments. Governments and private entities are collaborating to strengthen local manufacturing capabilities, focusing particularly on advanced packaging for niche applications and strengthening the domestic supply chain resilience.

- Latin America, Middle East, and Africa (LAMEA): This region currently represents a smaller share of the global market but is exhibiting accelerating adoption, mainly driven by the expansion of local data centers and rising demand for consumer electronics. Growth in this region is largely dependent on imported finished packaged devices, but increasing telecommunications infrastructure investment creates opportunities for localized assembly and test services in the long term.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Advanced Packaging Market.- Taiwan Semiconductor Manufacturing Company Limited (TSMC)

- ASE Technology Holding Co., Ltd. (ASEH)

- Amkor Technology, Inc.

- Samsung Electronics Co., Ltd.

- Intel Corporation

- JCET Group Co., Ltd.

- Powertech Technology Inc. (PTI)

- United Microelectronics Corporation (UMC)

- King Yuan Electronics Co., Ltd. (KYEC)

- UTAC Holdings Ltd.

- Shinko Electric Industries Co., Ltd.

- Toshiba Corporation

- Broadcom Inc.

- IBM

- Deca Technologies

- S-Semi

- Tianshui Huatian Technology Co., Ltd.

- Hana Micron Inc.

- Chipbond Technology Corporation

- Fuji Electric Co., Ltd.

Frequently Asked Questions

Analyze common user questions about the Advanced Packaging market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is the primary difference between 2.5D and 3D advanced packaging?

2.5D packaging uses a silicon or organic interposer to connect multiple dies side-by-side horizontally, optimizing high-speed communication over short distances. 3D packaging, in contrast, stacks dies vertically using Through-Silicon Vias (TSVs) or hybrid bonding to achieve maximum density and minimal interconnect length, which is critical for High Bandwidth Memory (HBM) integration.

How does Fan-Out Wafer Level Packaging (FO-WLP) improve device performance?

FO-WLP allows the redistribution layer (RDL) to extend beyond the chip’s footprint, creating more space for I/O connections and eliminating the need for a traditional substrate. This results in a thinner package with superior electrical performance, reduced parasitic resistance, better thermal management, and lower overall manufacturing cost compared to flip-chip BGA for mobile applications.

Which industry segment drives the highest demand for 2.5D/3D ICs?

The High-Performance Computing (HPC) and Data Center segment, encompassing AI accelerators, cloud server CPUs, and advanced networking processors, drives the highest demand for 2.5D/3D ICs. These technologies are essential for integrating high-capacity High Bandwidth Memory (HBM) directly with logic dies to meet the immense data throughput requirements of modern AI models.

What role does the Universal Chiplet Interconnect Express (UCIe) play in the advanced packaging ecosystem?

UCIe is a crucial standard designed to ensure interoperability between chiplets from different vendors. By standardizing the physical and protocol layers for die-to-die interconnects, UCIe enables the adoption of chiplet-based system architectures, reducing design complexity and fostering a modular, multi-vendor semiconductor supply chain, thereby accelerating the utilization of advanced packaging techniques.

What is the main restraint affecting the accelerated adoption of 3D integration technologies?

The primary restraint is the complexity and associated cost of manufacturing, particularly achieving high yields with Through-Silicon Vias (TSVs) and managing the critical thermal dissipation challenges inherent in vertically stacked active dies. High capital investment in specialized bonding and metrology equipment also acts as a significant barrier to entry for smaller market players.

To check our Table of Contents, please mail us at: sales@marketresearchupdate.com

Research Methodology

The Market Research Update offers technology-driven solutions and its full integration in the research process to be skilled at every step. We use diverse assets to produce the best results for our clients. The success of a research project is completely reliant on the research process adopted by the company. Market Research Update assists its clients to recognize opportunities by examining the global market and offering economic insights. We are proud of our extensive coverage that encompasses the understanding of numerous major industry domains.

Market Research Update provide consistency in our research report, also we provide on the part of the analysis of forecast across a gamut of coverage geographies and coverage. The research teams carry out primary and secondary research to implement and design the data collection procedure. The research team then analyzes data about the latest trends and major issues in reference to each industry and country. This helps to determine the anticipated market-related procedures in the future. The company offers technology-driven solutions and its full incorporation in the research method to be skilled at each step.

The Company's Research Process Has the Following Advantages:

- Information Procurement

The step comprises the procurement of market-related information or data via different methodologies & sources.

- Information Investigation

This step comprises the mapping and investigation of all the information procured from the earlier step. It also includes the analysis of data differences observed across numerous data sources.

- Highly Authentic Source

We offer highly authentic information from numerous sources. To fulfills the client’s requirement.

- Market Formulation

This step entails the placement of data points at suitable market spaces in an effort to assume possible conclusions. Analyst viewpoint and subject matter specialist based examining the form of market sizing also plays an essential role in this step.

- Validation & Publishing of Information

Validation is a significant step in the procedure. Validation via an intricately designed procedure assists us to conclude data-points to be used for final calculations.

×

Request Free Sample:

Related Reports

- IC Advanced Packaging Equipment Market Size By Region (North America, Europe, Asia-Pacific, Latin America, Middle East and Africa), By Statistics, Trends, Outlook and Forecast 2026 to 2033

- Advanced Packaging Materials Market Statistics 2025 Analysis By Application (Power Amplifier, Microwave Electronics, Thyristor, IGBT, MOSFET), By Type (Silicon Carbide (SiC), Aluminum nitride (AlN), Aluminum Silicon Carbide (AlSiC)), and By Region (North America, Latin America, Europe, Asia Pacific, Middle East, and Africa) - Size, Share, Outlook, and Forecast 2025 to 2032

- Advanced Packaging Inspection Systems Market Statistics 2025 Analysis By Application (Consumer Electronics, Automotive Electronics, Industrial, Healthcare), By Type (Optical Based Packaging Inspection Systems, Infrared Packaging Inspection Systems), and By Region (North America, Latin America, Europe, Asia Pacific, Middle East, and Africa) - Size, Share, Outlook, and Forecast 2025 to 2032

- Advanced Packaging Market Statistics 2025 Analysis By Application (Automotives, Computers, Communications, LED, Healthcare), By Type (3.0 DIC, FO SIP, FO WLP, 3D WLP, WLCSP, 2.5D, Filp Chip), and By Region (North America, Latin America, Europe, Asia Pacific, Middle East, and Africa) - Size, Share, Outlook, and Forecast 2025 to 2032

Select License

Why Choose Us

We're cost-effective and Offered Best services:

We are flexible and responsive startup research firm. We adapt as your research requires change, with cost-effectiveness and highly researched report that larger companies can't match.

Information Safety

Market Research Update ensure that we deliver best reports. We care about the confidential and personal information quality, safety, of reports. We use Authorize secure payment process.

We Are Committed to Quality and Deadlines

We offer quality of reports within deadlines. We've worked hard to find the best ways to offer our customers results-oriented and process driven consulting services.

Our Remarkable Track Record

We concentrate on developing lasting and strong client relationship. At present, we hold numerous preferred relationships with industry leading firms that have relied on us constantly for their research requirements.

Best Service Assured

Buy reports from our executives that best suits your need and helps you stay ahead of the competition.

Customized Research Reports

Our research services are custom-made especially to you and your firm in order to discover practical growth recommendations and strategies. We don't stick to a one size fits all strategy. We appreciate that your business has particular research necessities.

Service Assurance

At Market Research Update, we are dedicated to offer the best probable recommendations and service to all our clients. You will be able to speak to experienced analyst who will be aware of your research requirements precisely.

Contact With Our Sales Team

Customer Testimonials

The content of the report is always up to the mark. Good to see speakers from expertise authorities.

Privacy requested , Managing Director

A lot of unique and interesting topics which are described in good manner.

Privacy requested, President

Well researched, expertise analysts, well organized, concrete and current topics delivered in time.

Privacy requested, Development Manager